### About the Conference

#### About the Conference

The 39th Design Automation Conference is a high quality professional forum for technology interchange among design automation researchers and developers, the engineers who use DA systems to design, test and manufacture circuits and systems, and the vendors who provide both electronic design automation (EDA) systems and silicon. Five full days of activities are planned, including a rich technical program of research and case study papers, panels and tutorials, and an exhibition of the latest in EDA products and services. The conference this year will again highlight the convergence of embedded systems software design tools and EDA hardware design tools in support of large complex systems on a chip. This is reflected in the "Embedded Systems Showcase" on the exhibit floor, a panel session on "Unified Tools for SoC Embedded Systems", the Thursday keynote address by Jerry Fiddler, Chairman and Founder of Wind River, and a number of technical sessions sprinkled throughout the program.

The Technical Program consists of panel discussions, special (invited paper) sessions, and technical paper sessions. The Tuesday morning keynote will be presented by Dr. Hajime Sasaki, Chairman of the NEC Corporation, speaking on new challenges likely to be faced by the CAD industry. From there, the technical program is organized around two tracks. The Design Tools track focuses on new techniques for enhancing the performance and capabilities of EDA tools. The Design Methods track focuses on the results and insights gained by applying EDA tools to actual system designs. There are eight panel discussions

covering topics that range from the relationship between Wall Street and the EDA industry, to "What is the next EDA Driver" to "Tools or Users: Which is the Bigger Bottleneck?" The technical program also features 15 invited presentations by experts in their field, covering exciting topics such as "How do You a Design 10M Gate ASIC" to EDA tools for opto-electronics.

More than 200 companies will exhibit the latest commercially available products Monday through Wednesday. Demo suites provide an opportunity to more closely examine the offerings of particular vendors. For the first time this year, we will be featuring "Handson" Tutorials, Monday through Thursday, where vendors will have the opportunity to instruct small groups in the capabilities and use of their tools. The theme for these tutorials this year is "Verification of Embedded Systems".

On Monday, prior to the technical program, we will feature a tutorial for EDA professionals wanting to learn more about the world of embedded system software. Also on Monday, there will be an opportunity for non-technical attendees (teachers, financial community, spouses, etc.) to get a basic introduction to the world of EDA. On Friday the conference concludes, as usual, with five full-day specialized tutorials.

We invite you to join us in New Orleans and take full advantage of this rich and varied program.

### Important Information At-A-Glance

| Exhibit | Hours: | Demo | Suite | Hours: | Free | Monday | Exhibit-Only | Passes |

|---------|--------|------|-------|--------|------|--------|--------------|--------|

|         |        |      |       |        |      |        |              |        |

to 9:00 PM

to 9:00 PM

to 9:00 PM

to 5:00 PM

| Monday, June 10    |

|--------------------|

| Tuesday, June 11   |

| Wednesday, June 12 |

| Thursday, June 13  |

| 10:00 | AM | to | 6:00 | PM | 8:00 | AM |

|-------|----|----|------|----|------|----|

| 10:00 | ΑM | to | 6:00 | PM | 8:00 | AM |

| 10:00 | MΑ | to | 6:00 | PM | 8:00 | AM |

|       |    | _  |      |    | 8:00 | AM |

Register by May 24, 2002, and receive your badge via the US mail for immediate access to the exhibit hall at 10:00 AM, June 10, 2002. Call (800) 321-4573 or (303) 530-4333, or visit the DAC web site at www.dac.com.

### At-Conference Registration Hours

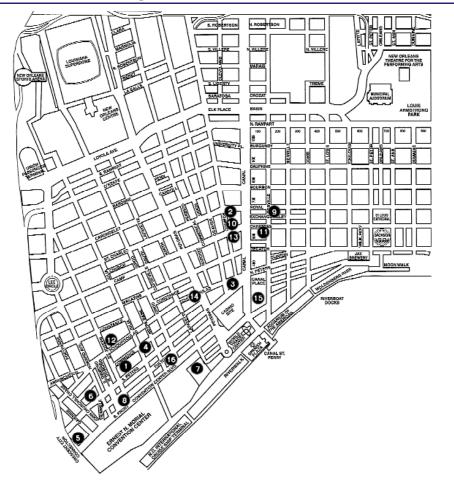

To avoid long lines register in advance by May 20, 2002. The registration desk will be located in the lobby of Halls H & I of the Ernest N. Morial Convention Center and will be open at the following times:

| Sunday, June 9, 2002     | 12:00 PM to 4:00 PM |  |

|--------------------------|---------------------|--|

| Monday, June 10, 2002    | 8:00 AM to 6:00 PM  |  |

| Tuesday, June 11, 2002   | 7:30 AM to 5:00 PM  |  |

| Wednesday, June 12, 2002 | 7:30 AM to 5:00 PM  |  |

| Thursday, June 13, 2002  | 7:30 AM to 3:00 PM  |  |

Tutorial Registration ......Friday, June 14, 8:00 AM to 1:00 PM

### **Uirtual DAC (www.dac.com)**

Virtual DAC offers two powerful on-line tools for attendees to make the most of their time at DAC. The "DAC Floor" is designed to allow attendees to plan the exhibitors they want to visit. The "DAC Planner" is designed for attendees to plan which technical sessions and other important DAC events they want to attend. Together the two services allow attendees to organize, in advance, how they want to utilize their time at DAC.

### **DACnet-2002**

DACnet stations will be located on the second level outside the auditorium of the Ernest N. Morial Convention Center.

| The 39th Design Automation Conference Week in Review |                                                                         |                                                                                        |                    |                   |                      |  |  |  |  |

|------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------|-------------------|----------------------|--|--|--|--|

| Sunday, June 9                                       | Monday, June 10                                                         | Tuesday, June 11                                                                       | Wednesday, June 12 | Thursday, June 13 | Friday, June 14      |  |  |  |  |

| 1                                                    | <ul><li>Hands-On Tutorials</li><li>Workshops</li><li>Exhibits</li></ul> | <ul><li>Opening Session</li><li>Technical Sessions</li><li>Hands-On Tutorial</li></ul> | • Exhibits         | 1 -               | • Full Day Tutorials |  |  |  |  |

### New @ DAC

#### DAC Pavilion

DAC brings its technical program to the exhibit floor through live panel discussions and broadcasts of highlighted technical sessions in the DAC Pavilion. DAC attendees and exhibitors are invited to visit the DAC Pavilion to participate in these engaging technical presentations or take a few minutes to relax in our lounge space.

#### A Whole NEW Monday at DAC

Monday at DAC has a whole new look this year. Exhibitor Presentations can now be found on each exhibitor's virtual DAC booth at www.dac.com. This has opened up Monday for workshops on Interoperability, Women in DA and an introductory session on EDA for non-engineers. If tutorials are more your flavor, check out the two Hands-On Tutorials or the Full-Day Tutorial on issues on embedded systems for EDA developers. In addition, the free Monday exhibit passes are still available. Monday at DAC is not to be missed!

#### **Tutorials**

DAC offers several new tutorial programs this year. Starting on Monday, June 10, there is a full-day introductory tutorial on An Introduction to Embedded Software: Issues, Tools and Methods - For HW and EDA Designers. This tutorial is designed to prepare attendees for the many embedded systems technical sessions offered in the technical sessions. The other new tutorial program at DAC this year is the Hands-on Tutorials.

#### Hands-On Tutorials

Hands-on Tutorials are half-day sessions offered by exhibitors demonstrating solutions to verifying embedded systems. These highly interactive sessions give attendees the opportunity to do in-depth software demonstrations on Sun workstations.

Monday 9:00 AM - 12:00 PM

Developing Bus-Functional Models for Embedded ATM Switch Verification • SynaptiCAD Inc., Synopsys, Inc.

Monday 2:00 PM - 5:00 PM

Creating and Using a Virtual Prototype for Embedded System Verification • Mentor Graphics Corp., Denali Software, Inc., AXYS Design Automation, Inc., Verisity Design, Inc.

Tuesday 2:00 PM - 5:00 PM

Assertion-Based Validation with HW/SW for Comprehensive Embedded System Verification

Co-Design Automation, Inc., Real Intent, ARM

Wednesday 9:00 AM - 12:00 PM

Hardware-Software Integration on the ARM Wireless PrimeXsys Platform using the CoWare N2C Design System • CoWare, Inc., ARM

Wednesday 2:00 PM - 5:00 PM

Verification of Embedded Communication Systems

• Cadence Design Systems, Inc., Xilinx, Inc., Synplicity, Inc.

Thursday 9:00 AM - 12:00 PM

Hardware and Software Debug Methods for a Programmable System • Xilinx, Inc., Wind River

Thursday 2:00 PM - 5:00 PM

Top-Level Validation of Complex SoCs • Esterel Technologies

### Program Highlights

#### **Technical Program** - details on pgs. 8 - 35

The technical program covers over 160 papers, panels and special sessions in five parallel tracks covering system level design, synthesis, physical design, verification, interconnect, power and AMS issues. Highlights include a focus on embedded systems (see right) as well as a number of special sessions with invited paper presentations on the implications of optics for EDA, the future of CMOS scaling, and designing 10M Gate ASICs.

**TUESDAY KEYNOTE** Chairman of the Board Hajime Sasaki

NEC Corp., Tokyo, Japan Tuesday, June 11 - 9:00 AM Room: Conference Auditorium

THURSDAY KEYNOTE Chairman and Founder Jerru Fiddler

Wind River, Alameda, CA Room: Auditorium B Thursday, June 13 - 1:00 PM

### Best Paper Awards

Best Paper Awards of \$1000 each will be announced at the Tuesday morning General Session, Papers eligible for awards in this category are nominated by the Program Committee and selected by a referee process.

### On-Site Information Desk

The information desk will be located in the lobby of Hall I of the Ernest N. Morial Convention Center. (504) 670-4500.

#### Embedded Systems -

Sessions: 3, 15, 19, 20, 23, 31, 34, 40, 41, 45, 49, 54 Recognizing the increasing role of embedded software and IP in complex SoC designs, we have provided a special focus on embedded systems topics. Over 35 papers and panels will cover topics such as embedded compilation, hardware/software co-design, system modeling and power optimization. In addition, special invited sessions will discuss design automation for electronic textiles, designing SoCs for yield improvement, and energy efficiency in mobile computing.

### SIGDA Ph.D Forum **Tuesday, June 11** - details on pg. 69

A chance for Ph.D students and industry representatives to get together. Students get feedback on their research proposals; industry gets a chance to meet students and preview their work.

**Tutorials** - details on pgs. 36 - 41

Monday, June 10, 2002 • 9:00 AM - 5:00 PM

1) An Introduction to Embedded Software: Issues, Tools and Methods - for HW and EDA Designers

Friday, June 14, 2002 • 9:00 AM - 5:00 PM

- 2) Intellectual Property Design and Integration for SoCs

- 3) Modeling Technology for High Frequency Design

- 4) Using SystemC for System Level Modeling and Design

- 5) Physical Chip Implementation: Hot Spots and Best Practices

- 6) New Computing Platforms for Embedded Systems

### Exhibit Highlights

#### Exhibit Floor

Monday - Wednesday, June 10-12, 2002 10:00 AM - 6:00 PM Over 225 EDA, Silicon, IP and Embedded Systems companies participate in the DAC exhibition and demo suites. All exhibits and suites are located in Halls E-J of the Ernest N. Morial Convention Center.

The Embedded Systems Showcase offers exhibitors and attendees a highly focused area to display and view tools for the design of embedded systems-on-chip. Children under the age of 14 will NOT be allowed in the exhibit hall or demo suite area.

The latest innovations are at your fingertips with exhibitors highlighting their latest products.

| Exhibitor ListingPages !              | 50 - 5 | 51 |

|---------------------------------------|--------|----|

| Exhibitor Company DescriptionsPages ! |        |    |

| Hands-On Tutorials                    |        |    |

#### Demo Suites

Monday - Wednesday, June 10-12, 2002 .......8:00 AM - 9:00 PM Thursday, June 13, 2002 ......8:00 AM - 5:00 PM

- Demo Suites will be in Halls E, F & G of the Ernest N. Morial Convention Center.

- Exhibiting companies offer their customers private product demos within the Convention Center.

- Demo Suites are available by invitation only.

### Exhibit -Only Registration

- Free Monday Exhibit-Only Passes Attend the exhibition free of charge Monday June 10.

- \$40 exhibit-only registration will allow you to attend exhibits Monday through Wednesday.

- Call (800) 321-4573, or register on-line at www.dac.com.

#### **DAC Pavilion**

DAC is introducing the DAC Pavilion in booth 1035. The Pavilion offers live panel discussions with industry experts, broadcasts of selected technical sessions and a lounge area to relax. Join us as we bring DAC's world-class technical program to the exhibit floor! Please check the DAC web site for details on the Pavilion presentations.

#### New Exhibitors at DAC

DAC has always been the best place to see the industry's newest companies, and this year is no exception. With over 30 new exhibitors this year, DAC is the place to be to find out what the hot start-ups are up to. Among the companies participating in DAC for the first time are: (as of March 21, 2002)

AccelChip, Inc. Acreo Annapolis Micro Systems, Inc. Apex Design Systems, Inc. Astek Corp. elnfochips Inc. Emulation and Verification Engineering EverCAD Navigator Corp. Freehand DSP Golden Gate Technology HPL Korea Electronics Technology Institute MathWorks (The) Multigia Ltd.

Nature Worldwide

Technology Corp.

NEWS Design System

Open Core Protocol

International Partnership

Prosilog SA

PTC

Q Design Automation

Sandwork Design Inc.

Signal Integrity Software

Silicon Canvas, Inc.

StarNet Communications

Tempus Fugit, Inc.

UbiTech, Inc.

Zenasis Technologies, Inc.

### Tues day Keynote – Paradigm Shift in Semiconductor Design: Challenges on the CAD System

Hajime Sasaki

Chairman of the Board

NEC Corp., Tokyo, Japan

Tuesday, June 11, 2002, 9:00 AM - 10:00 AM

Room: Conference Auditorium

Abstract: Last year, the Semiconductor industry suffered the severest recession in its history, withering by 32%. There had been no case where the final market of electronic products itself shrank. Concurrently, there have been some symbolic events in the industry. First, Moore's Law has become uncertain. In order to maintain the law, we must come up with novel processes for each new generation. Secondly, vendors have begun to shift from mass-production oriented business schemes to the system LSI business. This shift to application specific devices requires a drastic review of the value chain.

Semiconductor design in the new era can be divided into three areas. Area 1 deals with the traditional design hierarchy, such as function design, logic design and layout design. In this area, a revolution in function design is especially required that is represented by C language-based design. Area 2 deals with the new challenges of pursuing shrink technology. We should be prepared for problems resulting from the application of new materials, represented by electric current leakage through the gate insulator. Also, interconnect structure is another challenging problem. The merger of design and process is the key. Area 3 deals with comprehensive issues such as IP management and mass production know-how.

The industry will become much more dependent on design. The challenge is how we should cultivate competitive designers both in

quantity and quality. The "design project leader" must cover all three areas above. The corporate structure of IDM does not carry a competitive advantage, as long as design and process is divided into further sub-segments. When the industry can provide a solution that best meets its customer's needs and niceties from every angle, the industry will take off again and reach a new prosperous stage.

Biography: After receiving a master's degree of engineering in the field of electrical engineering from the graduate school of the University of Tokyo in 1961, he joined NEC Corporation. He served as General Manager of the VLSI Development Division and General Manager of the Microcomputer Products Division before being elected to the Board of Directors in 1988. He was appointed Senior Executive Vice President in 1996 in charge of semiconductors operations, and in 1999 elected to his current position of Chairman of the Board. Mr. Sasaki received the commendation from the Minister of State for Science and Technology, as a person of scientific and technological merits in 1995. In 2000, he received the Third Millennium Medal from IEEE. Also he was elected as a member of NAE (National Academy of Engineering). In 2001, he received the Robert N. Noyce Medal from IEEE and was elected as an IEEE Life Fellow.

### System

### Thursday Keynote - Software and Silicon - Where's the Equilibrium?

Jerry Fiddler

Chairman and Founder

Wind River, Alameda, CA

Thursday, June 13, 2002, 1:00 PM - 1:45 PM

Room: Auditorium B

Abstract: Silicon, EDA, and embedded software companies have largely lived in different universes. Despite repeated predictions that they would move closer together, and some real attempts to do so, those predictions have mostly proved false. Now, however, technology and economic trends are making it necessary and inevitable that suppliers find new ways to solve our customers problems. The complexity of the devices being built require solutions that cross the comfortable boundaries of the past. This talk will examine the trends and problems driving this.

Biography: Fiddler co-founded Wind River in 1981 with David Wilner, a colleague from Fiddler's tenure at University of California's Lawrence Berkeley Laboratory. Since establishing Wind River, Fiddler has taken on whatever role was necessary, from chief and only programmer to president and chairman of the board. Today Wind River, with operations worldwide, is the market share leader in embedded technology and continues to innovate and define the market.

Beginning with his tenure at the University of California's Lawrence Berkeley Laboratory, Fiddler has earned a reputation as an expert in the design and implementation of real-time systems. His work at Berkeley Lab gave him the ability to approach problems from a broader perspective and also taught him how to determine the pieces needed to build a system to solve a problem, skills that are key in developing embedded technology. He has published and presented numerous papers and articles on embedded technology and the rise of hidden, or embedded, computers in everyday life.

Fiddler graduated from the University of Illinois with a double baccalaureate in music and photography, and he received an M.S. in computer science from the same institution. Fiddler continues to follow his love of music with a home music studio and his band, XAZ, for which he writes songs and plays acoustic, electric, and classical guitars, as well as guitar synthesizer.

# The 39th Design Automation Conference • June 10 - 14, 2002 • New Orleans, LA

### Monday, June 10, 2002

|        | Room 294                                                                                   | Room 293                                            | Room 285                       | Room 286-287                                                                                                                             | Room 288              |

|--------|--------------------------------------------------------------------------------------------|-----------------------------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| 9:00   | Tutorial 1                                                                                 | Hands-On Tutorial                                   |                                |                                                                                                                                          |                       |

| 10:00  | An Introduction to                                                                         | Developing Bus-Functional                           |                                |                                                                                                                                          | Introduction to Chips |

|        | Embedded Software:                                                                         | Models for Embedded                                 |                                |                                                                                                                                          | and EDA For a         |

|        | Issues, Tools and Methods -                                                                |                                                     |                                |                                                                                                                                          | General Audience      |

|        | for HW and EDA Designers                                                                   | SynaptiCAD Inc.,                                    |                                |                                                                                                                                          | 10:00 AM - 12:00 PM   |

| 12:00  |                                                                                            | Synopsys, Inc.                                      |                                |                                                                                                                                          |                       |

| 1:00 - | Lunch in Room 296                                                                          |                                                     |                                |                                                                                                                                          |                       |

| 1.00   |                                                                                            |                                                     | Interoperability               |                                                                                                                                          |                       |

| 2:00   | An Introduction to Embedded Software: Issues, Tools and Methods - for HW and EDA Designers | Mentor Graphics Corp.,  Denali Software, Inc., AXYS | Workshop<br>12:00 PM - 5:00 PM | Workshop for Women in<br>Design Automation: Silk<br>Purses and Sow's Ears:<br>Turning Obstacles<br>into Opportunity<br>1:00 PM - 5:00 PM |                       |

| 5:00   |                                                                                            | Design Automation, Inc.,<br>Verisity Design, Inc.   |                                |                                                                                                                                          |                       |

Exhibit Hours 10:00 AM - 6:00 PM / Demo Suite Hours 8:00 AM - 9:00 PM

$\hbox{Tutorial 1 - An Introduction to Embedded Software: Issues, Tools and Methods - for HW and EDA Designers \bullet see \ pg \ 36 } \\$

Hands-On Tutorial - Developing Bus-Functional Models for Embedded ATM Switch Verification

• SynaptiCAD Inc., Synopsys, Inc. • see pg 64

Hands-On Tutorial - Creating and Using a Virtual Prototype for Embedded System Verification

• Mentor Graphics Corp., Denali Software, Inc., AXYS Design Automation, Inc., Verisity Design, Inc. • see pg 65

Interoperability Workshop • see pg 45

Workshop for Women in Design Automation - Silk Purses and Sow's Ears: Turning Obstacles into Opportunity • see pg 44 Introduction to Chips and EDA For a General Audience • see pg 43

### Tuesday, June 11, 2002

8:30 to 10:00

### Opening Session and Keynote Speaker Location: Conference Auditorium Paradigm Shift in Semiconductor Design: Challenges on the CAD System **Hallme Sasaki** - Chairman of the Board, NEC Corp., Tokyo, Japan

|                      |                                                        |                                                           | BREAK 10:15 - 10:30                           |                                        |                                                                      |

|----------------------|--------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------|----------------------------------------|----------------------------------------------------------------------|

|                      | Auditorium B                                           | Room 292                                                  | Room 288                                      | Room 287                               | Room 285                                                             |

|                      | Session 1                                              | Session 2                                                 | Session 3                                     | Session 4                              | Session 5                                                            |

| 10:30<br>to<br>12:00 | <b>PANEL:</b> Wall Street<br>Evaluates EDA             | Web and IP<br>Based Design                                | Design Innovations for<br>Embedded Processors | Passive Model<br>Order Reduction       | New Perspectives<br>in Physical Design                               |

|                      |                                                        |                                                           | LUNCH 12:00 - 2:00                            |                                        |                                                                      |

|                      | Auditorium B                                           | Auditorium A                                              | Room 292                                      | Room 288                               | Room 287                                                             |

|                      | Session 6                                              | Session 7                                                 | Session 8                                     | Session 9                              | Session 10                                                           |

| 2:00<br>to<br>4:00   | PANEL: Tools or Users: Which is the Bigger Bottleneck? | SPECIAL SESSION: Life After CMOS: Imminent or Irrelevant? | Formal Verification                           | High Level<br>Specification and Design | Timing Abstraction                                                   |

|                      |                                                        |                                                           | BREAK 4:00 - 4:30                             |                                        |                                                                      |

|                      | Session 11                                             | Session 12                                                | Session 13                                    | Session 14                             | Session 15                                                           |

| 4:30<br>to<br>6:00   | SPECIAL SESSION:<br>E-Textiles                         | PANEL: Analog Intellectual<br>Property: Now? Or Never?    | Low-Power<br>System Design                    | Fabric-Driven<br>Logic Synthesis       | Memory Management and<br>Address Optimization in<br>Embedded Systems |

SIGDA Ph.D forum at the Ernest N. Morial Convention Center 6:00 PM - 8:30 PM Exhibit Hours 10:00 AM - 6:00 PM / Demo Suite Hours 8:00 AM - 9:00 PM

All Design Methods Sessions are shaded purple. Embedded Systems Sessions are shaded grey. Presenters will be available in room 283 for additional 20-minute question and answer periods after the session.

# The 39th Design Automation Conference • June 10 - 14, 2002 • New Orleans, LA

### Wednesday, June 12, 2002

|                      | Auditorium B                                                                                                           | Auditorium A                                        | Room 292                                                         | Room 288                                          | Room 287                                             |

|----------------------|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------|------------------------------------------------------|

|                      | Session 16                                                                                                             | Session 17                                          | Session 18                                                       | Session 19                                        | Session 20                                           |

| 8:30<br>to<br>10:00  | SPECIAL SESSION: Optics: Lighting the Way to EDA Riches?                                                               | <b>PANEL:</b> Nanometer Design:<br>What Hurts Next? | Novel DFT, BIST and<br>Diagnosis Techniques                      | Case Studies In Embedded<br>System Design         | Theoretical Foundations of<br>Embedded System Design |

|                      |                                                                                                                        |                                                     | BREAK 10:00 - 10:30                                              |                                                   |                                                      |

|                      | Session 21                                                                                                             | Session 22                                          | Session 23                                                       | Session 24                                        | Session 25                                           |

| 10:30<br>to<br>12:00 | Equivalence Verification                                                                                               | <b>PANEL:</b> Whither (or Wither) ASIC Handoff?     | Embedded Software<br>Automation: From<br>Specification to Binary | Applications of<br>Reconfigurable<br>Computing    | New Test Methods Targeting<br>Non-Classical Faults   |

|                      |                                                                                                                        |                                                     | LUNCH 12:00 - 2:00                                               |                                                   |                                                      |

|                      | Session 26                                                                                                             | Session 27                                          | Session 28                                                       | Session 29                                        | Session 30                                           |

| 2:00<br>to<br>4:00   | SPECIAL SESSION:<br>How Do You Design<br>a 10M Gate ASIC?                                                              | Power Distribution Issues                           | Advances In Synthesis                                            | Analog Synthesis &<br>Design Methodology          | Low-Power<br>Physical Design                         |

|                      |                                                                                                                        |                                                     | BREAK 4:00 - 4:30                                                |                                                   |                                                      |

|                      | Session 31                                                                                                             | Session 32                                          | Session 33                                                       | Session 34                                        | Session 35                                           |

| 4:30<br>to<br>6:00   | PANEL: Unified Tools for<br>SoC Embedded Systems:<br>Mission Critical,<br>Mission Impossible<br>or Mission Irrelevant? | Multi-Voltage,<br>Multi-Threshold Design            | Advanced Simulation<br>Techniques                                | Design Methodologies<br>Meet Network Applications | Advances in Analog<br>Modeling                       |

39th DAC Wednesday Night Party • 7:30 PM - 10:30 PM • Hilton New Orleans Riverside

Exhibit Hours 10:00 AM - 6:00 PM / Demo Suite Hours 8:00 AM - 9:00 PM

All Design Methods Sessions are shaded purple. Embedded Systems Sessions are shaded grey.

Presenters will be available in room 283 for additional 20-minute question and answer periods after the session.

### Thursday, June 13, 2002

|                      | Auditorium B                                             | Auditorium A                                                            | Room 292                                    | Room 288                                                                           | Room 287                                                           |

|----------------------|----------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------|------------------------------------------------------------------------------------|--------------------------------------------------------------------|

|                      | Session 36                                               | Session 37                                                              | Session 38                                  | Session 39                                                                         | Session 40                                                         |

| 8:30<br>to<br>10:00  | Advances in Timing and Simulation                        | PANEL: Formal Verification<br>Methods: Getting<br>Around the Brick Wall | Routing and Buffering                       | System on Chip Design                                                              | Timing Analysis and<br>Memory Optimization for<br>Embedded Systems |

|                      |                                                          |                                                                         | BREAK 10:00 - 10:30                         |                                                                                    |                                                                    |

|                      | Session 41                                               | Session 42                                                              | Session 43                                  | Session 44                                                                         | Session 45                                                         |

| 10:30<br>to<br>12:00 | Processors and Accelerators<br>For Embedded Applications | <b>PANEL:</b> What is the Next EDA Driver?                              | Cross-Talk Noise Analysis<br>and Management | Test Cost Reduction<br>for SoCs                                                    | Scheduling Techniques for<br>Embedded Systems                      |

|                      | Keynot                                                   | e – Software and Silicon –                                              | Where's the Equilibrium? •                  | 1:00 - 1:45 • Room: Auditoria                                                      | um B                                                               |

|                      |                                                          | Jerry Fiddlei                                                           | - Chairman and Founder                      | r, Wind River                                                                      |                                                                    |

|                      | Session 46                                               | Session 47                                                              | Session 48                                  | Session 49                                                                         | Session 50                                                         |

| 2:00<br>to<br>4:00   | SPECIAL SESSION: Designing SoCs for Yield Improvement    | Advances in SAT                                                         | Inductance and<br>Substrate Analysis        | Development of Processors<br>and Communication<br>Networks for<br>Embedded Systems | Moving Towards More<br>Effective Validation                        |

|                      |                                                          |                                                                         | BREAK 4:00 - 4:30                           |                                                                                    |                                                                    |

|                      | Session 51                                               | Session 52                                                              | Session 53                                  | Session 54                                                                         | Session 55                                                         |

| 4:30<br>to<br>6:00   | SPECIAL SESSION: Energy Efficient Mobile Computing       | Floorplanning<br>and Placement                                          | Circuit Effects in<br>Static Timing         | Design Space Exploration for Embedded Systems                                      | Behavioral Synthesis                                               |

Demo Suite Hours 8:00 AM - 5:00 PM

All Design Methods Sessions are shaded purple. Embedded Systems Sessions are shaded grey. Presenters will be available in room 283 for additional 20-minute question and answer periods after the session.

### Awards

### P.O. Pistilli Scholarships (ACSEE)

Scholarships will be awarded to seven high school students of under-represented minorities who will be pursuing a degree in Electrical Engineering or Computer Science.

#### Marie R. Pistilli Women in EDA Achievement Award

The third annual award will be presented to a recipient who has made significant contributions in helping women advance in the field of DA technology.

### Student Design Contest Awards

Awards will be announced for the Student Design Contest winners.

### Best Paper Awards

Best Paper Awards of \$1000 each will be announced at the Tuesday morning General Session. Papers eligible for awards in this category are nominated by the Program Committee and selected by a referee process.

### ACM/SIGDA Distinguished Service Award

- Steven P. Levitan Dept. of Electrical Engineering, Univ. of Pittsburgh, Pittsburgh, PA

- Cheng-Kok Koh Dept. of Electrical and Computer Engineering, Purdue Univ., West Lafayette, IN

### ACM/SIGDA Outstanding New Faculty Award

Charlie Chung-Ping Chen - Department of Electrical and Computer Engineering, Univ. of Wisconsin, Madison, WI

### Phil Kaufman Award

The award honors an individual who has contributed to creating or driving technology advances that have had measurable impact on the productivity of design engineers. The 2001 recipient:

Alberto L. Sangiovanni-Vicentelli - Univ. of California, Berkeley, CA

### 2002 IEEE Fellows

Georges G. Gielen - Katholieke Univ., Leuven, Belgium For contributions to computer-aided design and design automation of analog and mixed-signal integrated circuits and systems.

Sharad Malik - Princeton Univ., Princeton, NJ

For contributions to electronic design automation technic

For contributions to electronic design automation techniques in logic andembedded software synthesis.

**Lawrence T. Pileggi** - Carnegie Mellon Univ., Pittsburgh, PA For contributions to simulation and modeling of integrated circuits.

Kaushik Roy - Purdue Univ., West Lafayette, IN For contributions to the power-aware design of digital circuits.

Ellen June Yoffa - IBM Research, Yorktown Heights, NY For technical, professional, and business leadership in electronic design automation.

### Graduate Scholarships

This year 4 scholarships will be awarded, two funded by DAC, and two funded by IEEE/CAS:

Prof. Florin Balasa, Univ. of Illinois, Chicago, IL

Students: Sarat Chandra Maruvada, Karthik Krishnamoorthy Novel Exploration Techniques in Device-Level Placement for Analog and Radio Frequency Blocks

Prof. Dinesh K. Bhatia, Univ. of Texas, Dallas, TX

Students: Shankar Balachandaran, Parivallal Kannan

Congestion and Routability Estimation for Large ASICs

Prof. Krishnendu Chakrabarty, Duke Univ., Durham, NC Student: Lei Li

Algorithms and Tools for Plug-and-Play System-on-a-Chip Test Automation

Prof. Ingrid Verbauwhede, Univ. of California, Los Angeles, CA Student: Patrick Schaumont

Domain Specific Tools and Methods for Application in Security Processor Design

### Opening Session

**Opening Remarks:** Bryan Ackland - General Chair, 39th DAC

**Awards Presented By:** Robert Walker Giovanni De Micheli ACM/SIGDA Representative IEEE/CAS Representative

### **Opening Keynote Address:**

Paradigm Shift in Semiconductor Design: Challenges on the CAD System Hajime Sasaki - Chairman of the Board, NEC Corp., Irvine, CA

### **Awards/Scholarships**

- P.O. Pistilli Scholarships (ACSEE)

- · Marie R. Pistilli Women in EDA Achievement Award

- Graduate Scholarships

- Student Design Contest Awards

- 2002 IEEE Fellows

- ACM/SIGDA Distinguished Service Award

- ACM/SIGDA Outstanding New Faculty Award

- · Phil Kaufman Award

Tuesday June 11

> 8:30 to 10:00

Tuesday June 11

> 10:30 to 12:00

All speakers are denoted in **bold**

S - denotes short paper Session 1

#### PANEL: WALL STREET EVALUATES EDA

**CHAIR:** Aart de Geus - *Synopsys, Inc., Mountain View, CA* **ORGANIZERS:** Sharon Turnoy, Deirdre Hanford

The EDA sector is capturing unprecedented attention on Wall Street. With seven IPOs in 2001 alone and strong performance by the EDA "blue chips," the industry has gained new prominence with the capital markets. In this panel, Aart de Geus will moderate a discussion between representatives of the various constituencies who play a role in shaping Wall Street's opinion of EDA: financial analysts, portfolio managers, venture capitalists, CEOs, and the press.

Questions discussed will include: How do investors and analysts currently view EDA? What contributes to that perception? What factors drive EDA's current favor with Wall Street, and why is the sector "hot" compared to two to three years ago? How do we sustain that favor? Given the highly complex nature of our industry, how do investors decipher the strength of a particular EDA firm? Is EDA tied to the semiconductor industry's performance? What role does the press play in shaping the view?

#### 1.1 Wall Street Evaluates EDA

Moshe Gavrielov - Verisity Design, Inc., Mountain View, CA Richard Goering - EE Times, Felton, CA Lucio Lanza- Lanza Tech Ventures, Palo Alto, CA Vishal Saluja - J. & W. Seligman & Co., Inc., Palo Alto, CA Jay Vleeschhouwer - Merrill Lynch & Co. Inc., New York, NY Session 2

rm: Auditorium B

#### WEB AND IP BASED DESIGN

rm: 292

**CHAIR:** Gang Qu - *Univ. of Maryland, College Park, MD* **ORGANIZERS:** Ahmed A. Jerraya, Krzysztof Kuchcinski

Web created new opportunities for geographically distributed design process but at the same time it introduced a number of challenges. The first paper presents techniques for IP delivery using Java applets. The second paper proposes generic techniques for watermarking-based IP protection that is essentially applicable to an arbitrary optimization and design problem. The third paper enables simulation of a design in the web environment. The final paper makes design process more flexible by leveraging on engineering change methodology.

### 2.1 IP Delivery for FPGAs Using Applets and JHDL

Michael J. Wirthlin, Brian McMurtrey - Brigham Young Univ., Provo, UT

### 2.2 Watermarking Integer Linear Programming Solutions

Seapahn Megerian, Milenko Drinic, Miodrag Potkonjak - Univ. of California, Los Angeles, CA

### 2.38 Model Design using Hierarchical Web-Based Libraries

Fabrice Bernardi, Jean F. Santucci - Univ. of Corsica, Corte, France

### 2.4S Behavioral Synthesis via Engineering Change

Milenko Drinic - Univ. of California, Los Angeles, CA Darko Kirovski - Microsoft Research, Redmond, WA

Design Methods Sessions are shaded purple. Embedded Systems Sessions are shaded grey.

*Session 3* rm: 288

# DESIGN INNOVATIONS FOR EMBEDDED PROCESSORS

CHAIR: Vojin Zivojnovic - AXYS Design Automation, Inc., Irvine, CA ORGANIZERS: Grant E. Martin, Maiid Sarrafzadeh

This session presents a number of interesting innovations in design techniques for embedded processors. The first paper reveals a novel technique for mixing compiled-code and interpreted-code approaches to instruction-set simulation. The second paper introduces the idea of incorporating optimized hard ware for profiling memory. The final paper reduces instruction memory size using decompression hardware.

# 3.1 A Universal Technique for Fast and Flexible Instruction-Set Architecture Simulation

Achim Nohl, Gunnar Braun, Andreas Hoffmann, Oliver Schliebusch, Rainer Leupers, Heinrich Meyr -Aachen Univ. of Tech., Aachen, Germany

### 3.2 A Fast On-Chip Profiler Memory

Roman Lysecky, Susan Cotterell, Frank Vahid - Univ. of California, Riverside, CA

#### 3.3 Design of a One-Cycle Decompression Hardware for Performance Increase in Embedded Systems

Haris Lekatsas, Joerg Henkel - NEC Corp., Princeton, NJ Session 4

### PASSIVE MODEL ORDER REDUCTION

CHAIR: Jacob White - Massachusetts Institute of Tech., Cambridge, MA

ORGANIZERS: Jaijeet Roychowdhury,

Mustafa Celik

Three excellent papers are presented in this session, with the theme of rigorous approaches to linear passive MOR addressing important theoretical and practical issues. The first paper presents a framework for MOR based on generalized factors that includes popular methods like PRIMA as special cases. The second paper presents a convincing argument that causality is key to effective passive MOR of distributed systems. The final demonstrates that attentiveness to positive real properties ensures passivity in truncated balanced realizations.

#### 4.1 A Factorization-Based Framework for Passivity-Preserving Model Reduction of RLC Sustems

Qing Su, Venkataramanan Balakrishnan, Cheng-Kok Koh - *Purdue Univ., West Lafayette, IN*

# 4.2 Model Order Reduction for Strictly Passive and Causal Distributed Systems

Luca Daniel - Univ. of California, Berkeley, CA Joel R. Phillips - Cadence Design Systems, Inc., San Jose, CA

#### 4.3 Guaranteed Passive Balancing Transformations for Model Order Reduction

Joel R. Phillips - Cadence Berkeley Labs., San Jose, CA Luca Daniel - Univ. of California, Berkeley, CA, Miguel Silveira - INESC, Lisboa, Portugal Session 5

rm: 287

# NEW PERSPECTIVES IN PHYSICAL DESIGN

rm: 285

CHAIR: Steven Teig - Simplex Solutions, Inc., Sunnyvale, CA

ORGANIZERS: Ralph Otten, Timothy Kam

This session presents early, innovative examples of what promise to be some of the next trends in physical design.

#### 5.1 Uncertainty-Aware Circuit Optimization

Xiaoliang Bai - Univ. of California at San Diego, La Jolla, CA

Chandu Visweswariah, Philip N. Strenski - *IBM Corp., Yorktown Heights, NY*David J. Hathaway - *IBM Corp., Essex Junction, VT*

## 5.2 Congestion-Driven Codesign of Power and Signal Networks

Haihua Su, Jiang Hu - IBM Corp., Austin, TX Sachin S. Sapatnekar - Univ. of Minnesota, Minneapolis, MN Sani R. Nassif - IBM Corp., Austin, TX

## 5.3 On Metrics for Comparing Routability Estimation Methods for FPGAs

Parivallal Kannan - Univ. of Texas, Dallas, TX

### Tuesday June 11

2:00 to 4:00

All speakers are denoted in **bold**

**S** - denotes short paper

Session 6

rm: Auditorium B

# PANEL: TOOLS OR USERS: WHICH IS THE BIGGER BOTTLENECK?

CHAIR: Andrew B. Kahng - Univ. of California at San Diego, La Jolla, CA

ORGANIZER: Bob Dahlberg

As chip design becomes ever more complex, fewer design teams are succeeding. Who's to blame? On one hand, tools are hard to use, buggy, not interoperable, and have missing functionality. On the other hand, there is a wide range of engineering skills, and tools can be abused within flawed methodologies. This panel will quantify and prioritize the key gaps that must be addressed on both sides.

#### 6.1 Tools or Users: Which is the Bigger Bottleneck?

Ron Collett - Numetrics Management Systems, Inc., Santa Clara, CA

Patrick Groeneveld, - Magma Design Automation, Inc., Cupertino, CA

Lambert Van den Hoven - Philips Research Labs., Eindhoven, The Netherlands

Lavi Lev- Cadence Design Systems, Inc., San Jose, CA Nancy Nettleton - Sun Microsystems, Palo Alto, CA Paul Rodman - ReShape, Inc., Palo Alto, CA Session 7

rm: Auditorium A

# SPECIAL SESSION: LIFE AFTER CMOS: IMMINENT OR IRRELEVANT?

**CHAIRS:** Dennis Sylvester - Univ. of Michigan, Ann Arbor, MI Kaustav Banerjee - Stanford Univ., Stanford, CA

ORGANIZERS: Dennis Sylvester, Kaustav Banerjee

With the introduction of 90nm CMOS processes as early as the fourth quarter of this year, we are finally entering the heralded nanometer CMOS regime. In nanoscale CMOS, many fundamental questions now become more pressing: how far can we scale the traditional planar CMOS paradigm, what device technologies are in development that can potentially replace CMOS and when? This session addresses both evolutionary and revolutionary approaches to continuing along Moore's Law. We start with industrial perspectives on how to best extend the lifespan of CMOS as we know it with the latter half of the session devoted to more radical departures from today's devices.

#### 7.1 Life is CMOS: Why Chase the "Life-After"?

George Sery - Intel Corp., Santa Clara, CA

## 7.2 The Next Chip Challenge: Effective Methods for Viable Mixed Technology SoCs

H. Bernhard Pogge - IBM Microelectronics, Hopewell Junction, NY

## 7.3 Few Electron Devices: Towards Hybrid CMOS-SET Integrated Circuits

Adrian Ionescu - Swiss Federal Institute of Tech., Lausanne, Switzerland

# 7.4 Carbon naotube Field-Effect Transistors for Logic Applications

Richard Martel - IBM Corp., Yorktown Heights, NY

Design Methods Sessions are shaded purple. Embedded Systems Sessions are shaded grey.

### FORMAL VERIFICATION HIGH LEVEL SPE

rm: 292

Session 9

CHAIR: Yaron Wolfsthal - IBM Corp., Haifa, Israel ORGANIZERS: Carl Pixley, Karem Sakallah

The need and benefits of formal verification (FV) have been accepted for some time. The capacity of FV-based tools is still limited and in this session new technologies and methodologies are presented that enable larger designs to be formally verified. In particular, novel ideas to enhance symbolic simulation, hybrid approach that uses symbolic simulation and model checking and SAT and BDD bounded model-checking.

### 8.1 Efficient State Representation for Symbolic Simulation

Valeria Bertacco, Kunle Olukotun - Stanford Univ., Stanford, CA

### 8.2 Handling Special Constructs in Symbolic Simulation

Alfred Koelbl - Tech. Univ. of Munich, Munich, Germany James Kukula - Synopsys, Inc., Beaverton, OR Kurt Antreich - Tech. Univ. of Munich, Munich, Germany Robert Damiano - Synopsys, Inc., Beaverton, OR

#### 8.3 A Hybrid Verification Approach: Getting Deep Into the Design

Scott Hazelhurst - Univ. of the Witwatersrand, Johannesburg, S. Africa Osnat Weissberg, Gila Kamhi, Limor Fix - Intel Corp.,

Haifa, Israel

8.4 Can BDDs Compete with SAT Solvers on Bounded Model Checking?

Gianpiero Cabodi, Paolo E. Camurati, Stefano Quer - Politecnico di Torino, Turin, Italy

HIGH LEUEL SPECIFICATION AND DESIGN

rm: 288

CHAIR: Andreas Kanstein - Motorola, Inc., Austin, TX

ORGANIZERS: Limor Fix, Shin-ichi Minato

With increasing design complexity, different technologies have been developed to bridge the gap between the amount of logic that can be put on a chip and the design and verification effort necessary to build such a chip. In this session, C-based design methodology is presented. High level specification is used for generation of IP monitors, for designing pipeline control and for constraining the design environment.

#### 9.1 C-Based RTL Methodology for Designing and Verifying a Multi-Threaded Processor

Luc Semeria, Andrew Seawright, Renu Mehra, Daniel Ng, Arjuna Ekanayake, Barry Pangrle -Clearwater Networks, Los Gatos, CA

## 9.2 High -Level Specification and Automatic Generation of IP Interface Monitors

Marcio T. Oliveira, Alan J. Hu - Univ. of British Columbia, Vancouver, British Columbia

# 9.3 Achieving Maximum Performance: A Method for the Verification of Interlocked Pipeline Control Logic

Kerstin I. Eder - Univ. of Bristol, Bristol, Great Britain Geoff Barrett - Broadcom Corp., Bristol, Great Britain

# 9.4 Formal Verification of Module I nterfaces Against Real Time Specifications

Arindam Chakrabarti - Univ. of California, Berkeley, CA Pallab Dasgupta, Partha P. Chakrabarti, Ansuman Banerjee - Indian Institute of Tech., Kharagpur, India Session 10

### TIMING ABSTRACTION

CHAIR: Mark Hahn - Cadence Design Systems, Inc., San Jose, CA ORGANIZERS: Chandu Visweswariah, Narendra V. Shenoy

Hierarchical timing verification and re-use of IP blocks require accurate timing abstraction. The first three papers of this session present various approaches to efficient generation of timing abstractions. The last paper applies ATPG and implication techniques to automatically detect multicycle paths in seguential circuits.

#### 10.1 Automated Timing Model Generation

Ajay J. Daga, Loa Mize, Subramanyam Sripada, Chris Wolff, Qiuyang Wu - Synopsys, Inc., Hillsboro, OR

## 10.2 Timing Model Extraction of Hierarchical Blocks by Graph Reduction

Cho Moon - Cadence Design Systems, Inc., San Diego, CA Harish Kriplani, Krishna P. Belkhale - Cadence Design Systems, Inc., San Jose, CA

#### 10.3 Efficient Stimulus Independent Timing Abstraction Model Based on a New Concept of Circuit Block Transparency

Martin Foltin, Brian Foutz, Sean C. Tyler - Hewlett-Packard Co., Fort Collins, CO

#### 10.4 An Implication-Based Method to Detect Multi-Cycle Paths in Large Sequential Circuits

Hiroyuki Higuchi - Fujitsu Labs. Ltd., Kawasaki, Japan rm: 287

Tuesday June 11

> 4:30 to 6:00

All speakers are denoted in **bold**

**S** - denotes short paper

Session 11

### SPECIAL SESSION: E-TEXTILES

rm: Auditorium B

CHAIR: Majid Sarrafzadeh - Univ. of California, Los Angeles, CA

ORGANIZER: Majid Sarrafzadeh

Topics: Enabling technologies and fabrication techniques for the economical manufacture of large-area, flexible, conformable etextiles applications. E-textiles represents a revolutionary step by bringing together textiles and electronics in a common effort to integrate many elementary sensors, actuators, logic, and power sources sparsely distributed application, with highly unreliable behavior, but with stringent constraints on operational longevity. On-the-fly reconfigurability and adaptability with low computational overhead. Device and technology challenges imposed by embedding simple computational elements into fabric, by building yarns with computational capabilities, or by the need of unconventional power sources.

# 11.1 Electronic Textiles: Large Area Sensing and Actuation

Elana Ethridge - DARPA, Arlington, VA

#### 11.2 The Wearable Mother board: A Framework for Personalized Mobile Information Processing (PMIP)

Sungmee Park, Ken Mackenzie, **Sundaresan Jayaraman** - Georgia Tech., Atlanta, GA

## 11.3 Opportunities and Challenges In E-textile Modeling, Analysis and Optimization

Diana Marculescu, Radu Marculescu, Pradeep Khosla -Carnegie Mellon Univ., Pittsburgh, PA Session 12

# PANEL: ANALOG INTELLECTUAL PROPERTY: NOW? OR NEVER?

rm: Auditorium A

CHAIR: Stephen Ohr - EET/CMP Media, San Francisco, CA ORGANIZERS: Linda Marchant, Philippe Magarshack

With more and more Systems-on-chip makers hoping to include analog functional blocks as a means of differentiating their designs, it is therefore tempting to believe that analog intellectual properties (IP) can be created, traded and integrated with the same tools and methodologies with which digital IP are moved about. But is analog IP a viable business? Can analog IPs be traded — given that design tuning is needed for every new chip variant, and every new process generation? Certainly, silicon foundries need to rely on a wide set of external IP offerings, in order to allow their users to build complete systems. Are they seeing enough activity in Analog IP designs to justify specialized fab runs, or the kind of process tuning that would allow analog and digital IPs to coexist on the same chip? What is the future of analog designs at the very low voltage-swings coming with sub-100nm CMOS? What CAD tools are needed to help analog designers? Are newly emerging EDA technologies, designed to enhance analog design productivity, maturing rapidly enough to be accepted by designers? Certainly many Analog IP providers and Analog EDA tool vendors would argue that the answer is ves. However, how many 'traditional' analog designers would admit they are still using kit parts and breadboards — maybe Spice and manual IC layout techniques — today in their everyday job? This panel of experts — representing analog designers. analog EDA tool providers, silicon foundries and analog IP vendors — will address these issues, and provide a likely context for analog IP development and trade.

#### 12.1 Analog Intellectual Property: Now? or Never?

Masao Hotta - Hitachi Ltd., Gunma-ken, Japan Mike Brunolli - NurLogic Design, Inc., San Diego, CA Felicia James - Cadence Design Systems, Inc., San Jose, CA Rudolf Koch- Infineon Technologies AG, Munich, Germany Roy McGuffin - Antrim Design Systems, Inc., Scotts Valley, CA Andrew Moore - TSMC, San Jose, CA

#### rm: 292

Session 14

#### rm: 288

Session 15

rm: 287

#### LOW-POWER SYSTEM DESIGN

CHAIR: Giovanni De Micheli - Stanford Univ., Stanford, CA

ORGANIZERS: Renu Mehra, Enrico Macii

This session deals with system level power minimization using dynamic voltage scaling. The first paper describes task scheduling algorithms that minimize energy in a multiprocessor environment. The second paper describes task scheduling algorithms that maximize battery life. The third paper minimizes energy in a multiprocessor environment by allowing each loop nest to be executed with multiple process and shutting off unused processors.

# 13.1 Task Scheduling and Voltage Selection for Energy Minimization

Yumin Zhang - Synopsys, Inc., Mountain View, CA Xiaobo (Sharon) Hu, Danny Z. Chen - Univ. of Notre Dame, Notre Dame, IN

#### 13.2 Battery-Conscious Task Sequencing for Portable Devices Including Voltage/Clock Scaling

Daler Rakhmatov, Sarma Vrudhula - Univ. of Arizona, Tucson, AZ

Chaitali Chakrabarti - Arizona State Univ., Tempe, AZ

#### 13.3 An Energy Saving Strategy Based on Adaptive Loop Parallelization

Ismail Kadayif, Mahmut T. Kandemir - Penn State Univ., University Park, PA Mustafa Karakoy - Imperial College, London, Great Britain

#### FABRIC-DRIVEN LOGIC SYNTHESIS

CHAIR: Maciej Ciesielski - Univ. of

Massachusetts, Amherst, MA

ORGANIZERS: Malgorzata Marek-Sadowska,

Steven Nowick

Papers in this section discuss synthesis approaches which target specific fabrics. The first paper proposes a new regular layout structure and discusses logic synthesis for it. The second paper describes a modified Bellman-Ford algorithm for cycle stealing in FPGAs. The third paper shows how layout information can improve carry-save adder designs.

### 14.1 River PLAs: A Regular Circuit Structure

Fan Mo, Robert K. Brayton - Univ. of California, Berkeley, CA

### 14.2 Cycle Stealing Boosts FPGA Performance

William B. Andrews, Barry K. Britton, Xiaotao Chen - Lattice Semiconductor, Inc., Allentown, PA

Alfred E. Dunlop - Consultant, Murray Hill, NJ

John P. Fishburn - Agere Systems, Inc., Allentown, PA

Harold N. Scholz - Lattice Semiconductor, Inc.,

Allentown, PA

#### 14.3 Layout-Aware Synthesis of Arithmetic Circuits

Junhyung Um, Taewhan Kim - KAIST, Taejon, Korea

#### MEMORY MANAGEMENT AND ADDRESS OPTIMIZATION IN EMBEDDED SYSTEMS

**CHAIR:** Nikil Dutt - Univ. of California, Irvine, CA **ORGANIZERS:** Diederik Verkest, Luca Benini

Memory access and addressing is often a critical issue in embedded system design. The papers in this session describe approaches to reduce/eliminate memory bottlenecks.

#### 15.1 Automatic Data Migration for Reducing Energy Consumption in Multi-Bank Memory Systems

Victor M. De La Luz, Mahmut T. Kandemir -Penn State Univ., University Park, PA Ibrahim Kelev - UMIST, Manchester, UK

#### 15.2 Exploiting Shared Scratch Pad Memory Space in Embedded Multiprocessor Systems

Mahmut T. Kandemir - Penn State Univ., University Park, PA

J. Ramanujam - Louisiana State Univ., Baton Rouge, LA

Alok Choudhary - Northwestern Univ., Evanston, IL

## 15.3 Address Assignment Combined with Scheduling in DSP Code Generation

Yoonseo Choi, Taewhan Kim - KAIST, Taejon, Korea

Wednesday June 12

> 8:30 to 10:00

All speakers are denoted in **bold**

**S** - denotes short paper

Session 16

#### SPECIAL SESSION: OPTICS: LIGHTING THE WAY TO EDA RICHES?

**CHAIR:** Jaijeet Roychowdhury - Univ. of Minnesota, Minneapolis, MN

ORGANIZERS: Jaijeet Roychowdhury, Joel R. Phillips

O ptical communication has been a key enabler in the development of the Internet. Now it is being considered for onchip signalling and communication as well. What implications does optics hold for the future of chip design and of EDA? Have EDA and optical CAD anything in common? Can they benefit each other? We look into these questions in this special session, consisting of two invited lectures and a contributed paper. The first talk is an overview of optical systems and their use in communications. The second focuses on computer-aided design techniques in optical communications. The final presentation describes a fast technique for computing optical fields propagating in free space.

# 16.1 The Optical Internet and the Drive Towards Multifunctional Hybrid Optoelectronic Integration

Edward H. Sargent - Univ. of Toronto, Toronto, ON, Canada

#### 16.2 Computer Aided Design of Long-Haul Optical Fiber Transmission Systems

J. F. Maloney - PhotonEx Corp., Maynard, MA C. R. Menvuk - Univ. of Maryland, Baltimore, MD

# 16.3 A Fast Optical Propagation Technique for Modeling Micro-Optical Systems

**Timothy P. Kurzweg**, Steven P. Levitan, Jose A. Martinez, Mark Kahrs, Donald M. Chiarulli - *Univ. of Pittsburgh, Pttsburgh, PA*

Session 17

rm: Auditorium B

# PANEL: NANOMETER DESIGN: WHAT HURTS NEXT?

rm: Auditorium A

CHAIR: Lawrence T. Pileggi - Carnegie Mellon Univ., Pittsburgh, PA

ORGANIZERS: Rob A. Rutenbar, Andrew B. Kahng

Every year, the design and EDA communities are besieged by dire warnings about the impending doom of "design as we know it". Every year, another unpleasant physical effect from the evil depths of deep submicron physics surfaces, compromising our designs in new and vile ways. Every year, the same story: more nanometer woes. Rather than endorse a new winner in this year's race for the "next worst thing" from the nanometer arena, this panel gathers a set of world-class technology experts to debate what effects are hiding just around the next corner, waiting to pounce on the unwary tool or chip designer. Which among these is really the most important, when will it happen, and why?

#### 17.1 Nanometer Design: What Hurts Next?

Bob Brodersen - Univ. of California, Berkeley, CA Anthony Hill - Texas Instruments, Inc., Dallas, TX John Kibarian - PDF Solutions, San Jose, CA Desmond A. Kirkpatrick - Intel Corp., Hillsboro, OR Mitsumasa Koyanagi - Tohoku Univ., Sendai, Japan Mark Lavin - IBM Corp., Yorktown Heights, NY

Design Methods Sessions are shaded purple. Embedded Systems Sessions are shaded grev.

Session 18 rm: 292

#### **NOUEL DFT, BIST AND** DIAGNOSIS TECHNIQUES

**CHAIR:** Rathish Jayabharathi - Intel Corp., Folsom, CA

ORGANIZERS: Kwang-Ting (Tim) Cheng, T.M. Mak

This session presents several novel ideas on DFT, BIST and diagnosis. The first paper discusses a DFT technique that utilizes clock control to simplify ATPG. The second paper tackles diagnosis problems with the conventional MISR signatures. The third paper presents a DFT technique to accommodate unknown output values in a BIST scheme. The last paper explores the diagnosis capability of software-based self-test.

#### 18.1 Low-Cost Sequential ATPG with Clock-Control DFT

Miron Abramovici - Agere Systems, Inc., Murray Hill, NJ

Xiaoming Yu, Liz Rudnick - Univ. of Illinois, Urbana, IL

#### 18.2 Effective Diagnostics Through Interval Unloads in a BIST Environment

Peter Wohll - Synopsys, Inc., Williston, VT Greg Maston, John Waicukauski, Sanjay Patel -Synopsys, Inc., Beaverton, OR

#### 18.35 On Output Response Compression in the Presence of Unknown Output Values

Irith Pomeranz - Purdue Univ., West Lafayette, IN Sandip Kundu - Intel Corp., Austin, TX Sudhakar M. Reddy - Univ. of Iowa, Iowa City, IA

#### 18.4S Software-Based Diagnosis for Processors

Li Chen, Sujit Dey - Univ. of California at San Diego, La Jolla, CA

Session 19

rm: 288

# EMBEDDED SYSTEM DESIGN

Session 20

CHAIR: Wayne Wolf - Princeton Univ., Princeton, NJ

CASE STUDIES IN

ORGANIZERS: Anand Raghunathan, Xiaobo (Sharon) Hu

This session showcases case studies and experiences using application specific design methodologies in the design of embedded systems. The presentations include the design of a Viterbi decoder for wireless handsets, the use of a cost model for Hardware/Software co-design in the design of a digital camera, and the generation of efficient software for H.263 image compression.

#### 19.1 Design of a High-Throughput Low-Power IS95 Viterbi Decoder

Xun Liu, Marios C. Papaefthymiou - Univ. of Michigan, Ann Arbor, MI

#### 19.2 A Detailed Cost Model for Concurrent Use With Hardware/Software Co-Design

Daniel Ragan, Peter Sandborn - Univ. of Maryland, College Park, MD

Paul Stoaks - Foresight-Systems, Inc., Austin, TX

#### 19.3 Efficient Code Sunthesis from Extended Dataflow Graphs for Multimedia **Applications**

Hyunok Oh, Soonhoi Ha - Seoul National Univ., Seoul, Korea

### THEORETICAL FOUNDATIONS OF EMBEDDED SYSTEM DESIGN

rm: 287

CHAIR: Raiesh Gupta - Univ. of California. Irvine, CA

ORGANIZERS: Annette Reutter, Donatella Sciuto

This session presents three formal approaches dealing with performance analysis and refinement transformations in embedded systems design. The first paper introduces formal transformation methods for the refinement of an abstract model into an implementation model. The second paper presents a compositional approach to analyze the timing behavior of complex systems under different scheduling strategies. The final paper shows a new timing generation method for the performance analysis of embedded software.

#### 20.1 Transformation Based Communication and Clock Domain Refinement for System Design

Ingo Sander, Axel Jantsch - Royal Institute of Tech., Kista, Sweden

#### 20.2 Model Composition for Scheduling Analysis in Platform Design

Kai R. Richter, Dirk Ziegenbein, Marek Jersak, Rolf Ernst - Tech. Univ. of Braunschweig, Braunschweig, Germany

#### 20.3 Timed Compiled-Code Simulation of **Embedded Software for Performance** Analysis of SOC Design

Jong-Yeol Lee, In-Cheol Park - KAIST, Taejon, Korea

Wednesday June 12

> 10:30 to 12:00

All speakers are denoted in **bold**

**S** - denotes short paper

Session 21

### **EQUIVALENCE VERIFICATION**

CHAIR: Ziyad Hanna - Intel Corp., Haifa, Israel ORGANIZER: Shin-ichi Minato

Using equivalence checker to prove the functional equivalence of two designs is a common and practical verification approach. In this session, new technologies are presented that enable extraction of complex circuits, allows sequential equivalence and handle hard-to-verify arithmetic operators.

### 21.1 Automated Equivalence Checking of Switch Level Circuits

Atanas N. Parashkevov - Motorola, Inc., Mawson Lakes, Australia Simon Jolly - Foursticks Pty. Ltd., Frewville, Australia Tim McDougall - Motorola, Inc., Mawson Lakes, Australia

# 21.2 A Practical and Efficient Method for Compare-Point Matching

Demos Anastasakis, Robert Damiano - Synopsys, Inc., Hillsboro, OR

Hi-Keung T. Ma - Synopsys, Inc., Mountain View, CA

Ted Stanion - Synopsys, Inc., Hillsboro, OR

## 21.3 Self-Referential Verification of Gate-Level Implementations of Arithmetic Circuits

Ying-Tsai Chang, Kwang-Ting (Tim) Cheng - Univ. of California, Santa Barbara, CA

Session 22

rm: Auditorium B

# PANEL: WHITHER (OR WITHER?) ASIC HANDOFF

rm: Auditorium A

CHAIR: Michael Santarini - EE Times, San Mateo, CA ORGANIZERS: Mark Miller, Sudhakar Jilla

The traditional ASIC netlist handoff is changing - but to what? Is RTL handoff finally a reality? Or, will a placement-based handoff model emerge? Are differences among underlying tool technologies and methodologies only cosmetic? Or, are there fundamental business and IP distinctions? These and other questions will be discussed as the panel examines the future of the designer - ASIC vendor relationship.

#### 22.1 Whither (or Wither) ASIC Handoff?

Tommy Eng - Tera Systems, Inc., Campbell, CA Sandeep Khanna - Synopsys, Inc., Mountain View, CA Kamalesh Ruparel - Cisco Systems, Inc., Sarratoga, CA Tom Russell - IBM Microelectronics, Essex Junction, VT Kazu Yamada - NEC Corp., Santa Clara, CA

Design Methods Sessions are shaded purple. Embedded Systems Sessions are shaded grey.

rm: 292

Session 24

rm: 288

Session 25

# EMBEDDED SOFTWARE AUTOMATION: FROM SPECIFICATION TO BINARY

CHAIR: Joerg Henkel - NEC Corp., Princeton, NJ ORGANIZERS: Marco Di Natale, Xiaobo (Sharon) Hu

The increasing embedded software content of electronic systems makes it important to automate various aspects of the software design flow. This session presents papers that represent advances in embedded software automation, including synthesis from synchronous specifications, automatic library mapping for complex functions using symbolic algebra, and re-targetability of binary utilities.

# 23.1 Software Synthesis from Synchronous Specifications Using Logic Simulation Techniques

Yunjian Jiang, Robert K. Brayton - Univ. of California, Berkeley, CA

# 23.2 Complex Library Mapping for Embedded Software using Symbolic Algebra

Armita Peymandoust - Stanford Univ., Stanford, CA Tajana Simunic - Hewlett-Packard Labs., Palo Alto, CA Giovanni De Micheli - Stanford Univ., Stanford, CA

#### 23.3 Retargetable Binary Utilities

Maghsoud Abbaspour, Jianwen Zhu - Univ. of Toronto, Toronto, ON, Canada

# APPLICATIONS OF RECONFIGURABLE COMPUTING

CHAIR: Ivo Bolsens - Xilinx, Inc., San Jose, CA ORGANIZERS: Grant E. Martin, Kurt Keutzer

This session demonstrates that Reconfigurable Computing has come of age. The first paper looks at how multimedia applications will benefit through dynamic reconfiguration of operation level parallelism. The second one builds a case for partial runtime reconfiguration, demonstrated on a networking application. The final paper is a case study in which what might normally be a software testbench for disk drive design is instead built as reconfigurable hardware, giving much higher performance.

# 24.1 Exploiting Operation Level Parallelism through Dynamically Reconfigurable Datapaths

Zhining Huang, Sharad Malik - Princeton Univ., Princeton, NJ

# 24.2 Dynamic Hardware Plugins for FPGAs with Partial Run-Time Reconfiguration

Edson L. Horta - LSI-EPUSP-USP, Sao Paulo, Brazil John W. Lockwood - Washington Univ., St. Louis, MO Dave Parlour - Xilinx, Inc., San Jose, CA David Taylor - Washington Univ., St. Louis, MO

# 24.3 A Reconfigurable FPGA-Based Readback Signal Generator For HardDrive Read Channel Simulator

Jinghuan Chen, Jaekyun Moon, **Kia Bazargan** - Univ. of Minnesota, Minneapolis, MN

# NEW TEST METHODS TARGETING NON-CLASSICAL FAULTS

rm: 287

**CHAIR:** Rob Aitken - Agilent Technologies, Santa Clara, CA

ORGANIZERS: Miron Abramovici, T.M. Mak

Complexity of VLSI testing requires targeting new types of faults in addition to the classical stuck-at fault model. The session illustrates different aspects of this struggle.

#### 25.1 Embedded Tutorial: Embedded Software-Based Self-Testing for SoC Design

Angela Krstic, Wei Cheng Lai, Li Chen, Kwang-Ting (Tim) Cheng - Univ. of California, Santa Barbara, CA Sujit Dey - Univ. of California at San Diego, La Jolla, CA

#### 25.2 A Novel Wavelet Transform Based Translent Current Analysis for Fault Detection and Localization

Swarup K. Bhunia, Kaushik Roy - Purdue Univ., West Lafayette, IN Jaume Segura - Balearic Islands Univ., Mallorca, Spain

# 25.38 Signal Integrity Fault Analysis Using Reduced-Order Modeling

Amir Attarha, Mehrdad Nourani - Univ. of Texas, Richardson, TX

#### 25.4S Enhancing Test Efficiency for Delay Fault Testing Using Multiple-Clocked Schemes

Jing Jia Liou, **Li C. Wang**, Kwang-Ting (Tim) Cheng - *Univ. of California, Santa Barbara, CA*Jennifer Dworak, Ray Mercer - *Texas A&M Univ., College Station, TX*Tom Williams - *Synopsys, Inc., Boulder, CO*

Wednesday June 12

> 2:00 4:00

All speakers are denoted in **bold**

> S - denotes short paper

Session 26

rm: Auditorium B

#### SPECIAL SESSION: HOW DO YOU Design a 10m gate asic?

CHAIR: Ahmed A. Jerraya - TIMA Lab., Grenoble Cedex, France

ORGANIZERS: Ahmed A. Jerraya, Kurt Keutzer

ASIC design has always been challenging but an increasing number of design groups are unsuccessful at designs in excess of 4M logic gates. A leading industry analyst states that first-silicon success is only a tenth as likely at 10M gates as at lower complexity levels. Some designers have even claimed that design above the 4M logic gate complexity is simply impossible with the current generation of design tools. Nevertheless, a number of designers are successfully approaching the 10M gate complexity level. How are they doing it? In this session designers from three segments of the integrated-circuit design industry will describe key aspects of their design methodology that enable them to achieve silicon success on high complexity designs.

#### 26.1 Going Mobile: The Next Horizon for Multi-Million Gate Designs in the Semiconductor Industry

Christian Berthet - STMicroelectronics, Grenoble Cedex, France

#### 26.2 When 10M Gates Just Isn't Enough: The GPU Challenge

Chris Malakowsky - NVidea, Santa Clara, CA

#### 26.3 Challenges in achieving First-Silicon Success for 10M-Gate SoCs: A Silicon Engineering Perspective

Aurangzeb Khan - Simplex Solutions, Inc., Sunnyvale, CA

Session 27

rm: Auditorium A

#### POWER DISTRIBUTION ISSUES

CHAIR: Sachin Sapatnekar - Univ of Minnesota, Minneapolis, MN

ORGANIZERS: Abhijit Dharchoudhury, Tadahiro Kuroda

Power distribution issues are becoming extremely important as levels of integration increase. The first paper describes a model-order reduction method for hierarchical power grid analysis. The second paper describes a frequency-domain macromodel for block current signatures. The third paper describes circuit models for the chip interface, and the fourth paper describes a method for analyzing symmetrical P/G networks. The final paper describes a method to optimize clock distribution networks using supply current folding.