# ACM/EDAC/IEEE 45th DESIGN AUTOMATION CONFERENCE JUNE 8-13, 2008 • ANAHEIM, CA • WWW.DAC.COM

**Exhibits**

State-of-the-art Research

# **Final Program**

TOMATIONCONFERENCE

Breakthrough Technology

# **General Chair's Welcome**

## DAC: WHERE ELECTRONIC DESIGN MEETS...

# WELCOME TO THE 45TH DESIGN AUTOMATION CONFERENCE AND THE CITY OF ANAHEIM!

DAC is the premier event for the electronic design community. It offers the industry's most prestigious technical conference in combination with the biggest exhibition. DAC is also increasingly the meeting place for many related organizations — the conference this year has attracted a record number of additional events. In particular, 14 workshops and seven collocated events are taking place during DAC.

We are privileged to have as guest speakers, the ACM Turing Award winners, who have been recognized with the highest honor in the area of computing for their role in developing Model-checking into a highly effective verification technology, widely adopted in the hardware and software industries: Edmund M. Clarke, FORE Systems Professor, Carnegie Mellon University, E. Allen Emerson, Endowed Professor, University of Texas at Austin and Joseph Sifakis, CNRS Research Director, Verimag.

DAC is proud to present outstanding industry leaders in three keynote presentations. On Tuesday, Justin R. Rattner, Intel Senior Fellow, Vice President, Director, Corporate Technology Group and Chief Technology Officer, Intel Corp., will re-examine radio architecture and describe the expected shift from largely analog to nearly pure digital and programmable multi-radios design. On Wednesday, Sanjay K. Jha, Chief Operating Officer, Qualcomm and President, Qualcomm CDMA Technologies, will present the design challenges of advanced wireless silicon systems. His talk will focus on how partnering companies need to collaborate to tackle complex design issues through synergistic groups. On Thursday, Jack Little, President, and Co-founder of The MathWorks, Inc., will discuss the emerging workflow from idea to system implementation. Such a design flow will provide great value to companies that develop embedded systems and electronics.

DAC's 82 member Technical Program Committee selected 147 papers for this year's technical program from a pool of 639 submissions. Highlighted topics this year are Business, Design Methodologies, System Level and Embedded Design, Interconnect and Reliability, Synthesis and FPGA, Low Power, Multi-core, Wireless, Physical Design, DFM and the Manufacturing Interface, Analog/Mixed Signal/RF and Simulation, Verification and Test, Strictly Design and New and Emerging Technologies. The program also includes eight Panels, eight Special Sessions, six Tutorials and six Handson Tutorials, Management Day and WACI ("Wild and Crazy Ideas"). DAC's exhibition features over 225 companies and includes 20 exciting Pavilion Panels.

New this year are DAC's iDesign sessions, the DACeZine newsletter, the YouTube preview of the technical program, the Exhibitor Forum that offers a series of technical presentations from exhibitors, and the Best of DAC Contest, which invites you to vote for your favorite products and vendors.

Continuing DAC's 45-year tradition, the efforts of hundreds of volunteers — authors, speakers, session chairs, reviewers, session organizers, moderators, panelists, and members of the DAC Executive Committee, Technical Program Committee, Panel Committee, Exhibitor Liaison Committee, SDC Judges, Tutorial Committee, and Strategy Committee — have gone into making DAC the premier event for the electronic design community. Fantastic contributions are also made by all of the companies participating in DAC's exhibition and by DAC's management company, MP Associates, Inc. We are grateful for all of this support and in particular, we extend special thanks to our sponsors, ACM/SIGDA, IEEE/CASS/CANDE/CEDA, and the EDA Consortium.

We wish you a productive and exciting week at DAC!

Best regards,

Limor Fix

Limor Fix General Chair, 45th Design Automation Conference

# **INDEX**

| 46th DAC Call for Papers                    | 76 - 77 | Exhibitor Forum (Exhibit Hall D, Booth #2849)                 | 14 - 16   |

|---------------------------------------------|---------|---------------------------------------------------------------|-----------|

| Additional Meetings                         | 72 - 75 | Exhibitor Listing                                             | 90 - 91   |

| Adjunct Events                              | 70 - 71 | Exhibitor Supplemental Listing                                | 145 - 146 |

| ACM Turing Award Winners                    |         | General Chair's Welcome                                       |           |

| EDA Consortium Executive Reception          |         | General Session / Keynote Address                             | 23        |

| IEEE Council on EDA's Distinguished Speaker |         | Hands-on Tutorials                                            | 60 - 61   |

| SIGDA Ph.D Forum/Member Meeting             |         | Important Information At-a-Glance                             | 5         |

| Anaheim Welcome                             | 4       | • DACnet-2008                                                 |           |

| Anaheim Attractions                         |         | Exhibit hours                                                 |           |

| First-aid Rooms                             |         | Registration Hours                                            |           |

| Guest/Family Program                        |         | Stay Connected                                                |           |

| Hotel Locations                             |         | Tutorial Registration                                         |           |

| On-site Information Desk                    |         | Keynote Addresses                                             |           |

| Weather                                     |         | Tuesday Keynote Address                                       | 9         |

| Wednesday Night Party                       |         | Wednesday Keynote Address                                     | 10        |

| Awards                                      | 64      | Thursday Keynote Address                                      | 11        |

| Best of DAC                                 |         | Management Day                                                | 12 - 13   |

| Collocated Events                           |         | Pavilion Panels                                               |           |

| Committee List                              |         | Registration Hours                                            | 5         |

| Executive Committee                         |         | Sponsors                                                      | 62 - 63   |

| Exhibitor Liaison Committee                 |         | 45th DAC Proceedings DVD                                      |           |

| Panel Committee                             |         | <ul> <li>ACM/SIGDA</li> </ul>                                 |           |

| Strategy Committee                          |         | <ul> <li>Association for Computing Machinery (ACM)</li> </ul> |           |

| Student Design Contest Judges               |         | EDA Consortium                                                |           |

| Technical Program Committee                 |         | • IEEE                                                        |           |

| Tutorial Committee                          |         | IEEE/Circuits and Systems Society                             |           |

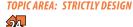

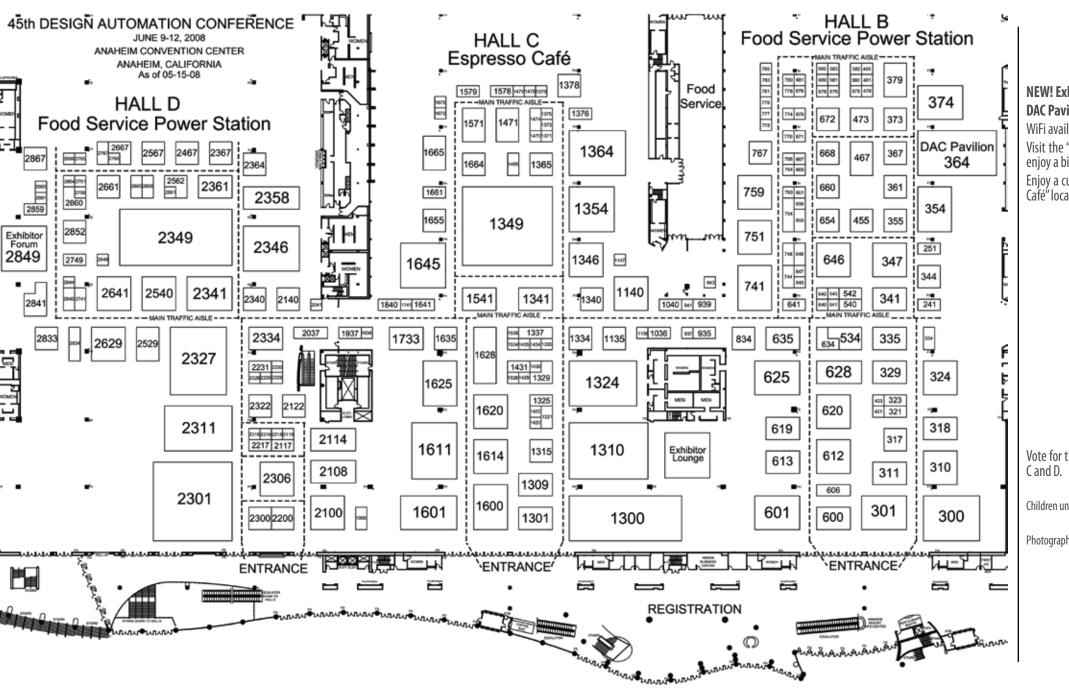

| Conference Floorplan                        | 06      | IEEE/Computer Aided Network Design                            |           |

| Conference Schedule                         |         | IEEE/Council on Electronic Design Automation                  |           |

| Exhibit Floorplan                           |         | SIGDA/DAC University Booth                                    |           |

| Exhibit Highlights                          |         | Student Design Contest                                        | 65        |

| Best of DAC                                 |         | Technical Program Highlights                                  |           |

| DAC Pavilion                                |         | Technical Sessions                                            |           |

| Exhibition Hours                            |         | Tutorials                                                     |           |

| Exhibitor Forum                             |         | Monday Tutorials                                              | 42        |

| IP, Design Services and Test Companies      |         | Friday Tutorials                                              |           |

| New Exhibitors                              |         | Wireless Theme                                                |           |

|                                             | r       | Workshops                                                     |           |

| Exhibit Hours                               |         |                                                               |           |

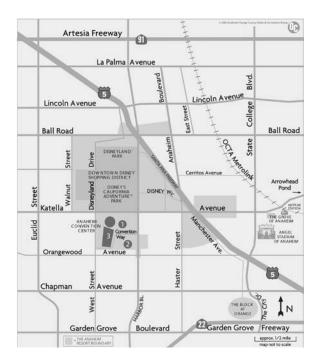

# Welcome to Anaheim

#### Weather

Anaheim is one of the few places in the world with a Mediterranean climate. The Anaheim Resort is an 1100-acre garden district that encompasses the With 355 days of sunshine every year, it is nearly guaranteed that you will experience a beautiful tropical day. Anaheim offers delightful ocean breezes, low humidity, and very little rain. The average high temperature in June is 77 degrees, cooling off at night to 59 degrees. Summer clothing is appropriate and a light jacket may be needed for the evenings.

#### First Aid Room

The First Aid Room is located in Lobby B of the Anaheim Convention Center. For assistance, please call ext. 8101; for an emergency call ext. 8080. A Hotel Locations nurse will be on duty at all times while meetings and exhibits are open. From a mobile phone, dial (714) 765-8950.

### **Guest/Family Program**

An \$80 registration fee will admit each guest or family member to the following:

- 1. Wednesday Night Party at the Anaheim Marriott in the Platinum Ballroom.

- 2. Admission to the exhibit hall (when accompanied by an attendee). Registration for the Guest/Family Program will be at the Conference Registration desk on Sunday, June 8 through Wednesday, June 11, 2008. A badge will be provided for each registered guest or family member. This badge must be worn to participate in the above activities.

- 3. Children under the age of 14 are not allowed in the exhibit hall area. A \$30 registration fee will allow access to the Wednesday Night Party only.

#### **On-site Information Desk**

The Information Desk will be located in the Main Lobby of the Anaheim Convention Center, Phone: (714) 765-2014.

#### Anaheim Attractions

redesigned and expanded Anaheim Convention Center and the Disneyland Resort, which features the original Disneyland (this year is their 53rd anniversary), the thrilling new theme park — Disney's California Adventure, and the lively Downtown Disney, a new shopping, dining, and entertainment district. For more information on the Anaheim Resort and Orange County, visit www.anaheimoc.org or call the Anaheim/Orange County Visitor and Convention Bureau at (714)765-8888.

- 1 Anaheim Marriott Hotel

- 2 Hilton Anaheim Hotel

# **Important Information At-a-Glance**

## **EXHIBIT HOURS**

| Monday, June 9     | 9:00am - 6:00pm |

|--------------------|-----------------|

| Tuesday, June 10   | 9:00am - 6:00pm |

| Wednesday, June 11 | 9:00am - 6:00pm |

| Thursday, June 12  | 9:00am - 1:00pm |

## REGISTRATION HOURS

| Sunday, June 8     | 8:00am - 6:00pm |

|--------------------|-----------------|

| Monday, June 9     | 7:00am - 6:00pm |

| Tuesday, June 10   | 7:00am - 6:00pm |

| Wednesday, June 11 | 7:00am - 6:00pm |

| Thursday, June 12  | -               |

| Friday, June 13    | •               |

## TUTORIAL REGISTRATION

### **Monday Tutorial Registration**

Register for Tutorials on Sunday and Monday at times above in Lobby B Conference Registration.

### **Friday Tutorial Registration**

## Friday, June 13 / 8:00am - 6:00pm

Tutorial Registration is located on the 2nd floor outside of Room 205AB.

# STAY CONNECTED AT DAC

#### Wireless Internet

DAC is offering complimentary wireless internet throughout the Anaheim Convention Center. Look for SSID: **DAC2008**.

### **Mobile Devices**

DAC has a special website built for viewing from handheld mobile devices. From your Windows Mobile or Blackberry device, log in to www.dac.com and you will be automatically redirected to the mobile site. Presentation schedules, the exhibitor listing and other useful information are available and optimized for viewing on small screens.

## Daily Updates on DAC.com

Check the DAC website daily for a complete listing of each day's schedule, latest exhibitor announcements, and press coverage.

### **Food Courts**

Two food courts and an espresso café are available on the exhibit floor. Each food court includes tables with power connections for laptop plug-in.

### **DACnet - 2008**

DACnet internet stations are available in Lobby D and on the  $2^{nd}$  floor next to room 213A. Power for laptop plug-in is also available at both locations.

## WEDNESDAY NIGHT PARTY

## Wednesday, June 11 / 7:30 - 10:00pm

Please join us at the Anaheim Marriott Hotel in the Platinum Ballroom for the 45th DAC Wednesday Night Party! There will be a wide array of delectable foods along with plentiful amounts of wine, beer, and assorted beverages. This year DAC is proud to present The Zippers. Since their beginning as champions on Ed McMahon's StarSearch, the Zippers have performed to rave audiences the world over. Now featuring the addition of two incredibly talented female vocalists, the Zippers have achieved a new level that can only be described as spectacular. They are flashy, energetic, funny, and guaranteed to make you want to dance all night long. Entertainment begins at 8:00pm as The Zippers take you on a musical journey. Don't miss the fun! This is sure to be a memorable experience!

To join these festivities, you must register as a student or full conference attendee. You may also register for the Guest/Family Program.

# **60**

# Technical Program Highlights

This year's technical program is especially strong, consisting of 147 papers selected from 639 submissions, with Wild and Crazy Ideas (WACIs) and the popular panels and special sessions to round it out. The program, intended for design engineers, management, researchers and developers, showcases the latest results and emerging trends in the design of electronic circuits and systems, and Electronic Design Automation (EDA).

On Tuesday, the "iDesign" Track has been added. The first session will address how to build a practical physical implementation flow, while the second session offers hands-on aspects of SystemVerilog, the Verification Methodology Manual for SystemVerilog (VMM) and Open Verification Methodology (OVM). This year's conference theme is "Wireless", highlighted by an all-day track of sessions on Wednesday, including a panel that will identify who's ready for next-generation wireless multimedia devices, and a special session titled "Business Meets Technology."

In the 36 technical paper sessions, topics range from system-level design and design for manufacturing (DFM) to verification and emerging technologies. At DAC 2008 there is ample opportunity to discuss the emergence of multi-core systems. Speakers will discuss the latest in acceleration of circuit simulation on multi-threaded processors, and how to improve fault simulation on graphics processing units (GPUs).

A special session highlights issues related to the use of multi-cores for general-purpose as well as EDA applications. This is followed by a two-part panel; the first paper examines the outlook for EDA on multi-cores, providing the perspective of the major EDA vendors, while the second addresses the design of multi-core systems. Other sections of the technical program will illustrate how embedded systems are going multi-core as well, and present design tools to optimize embedded applications. A practical session for the verification engineer details how to achieve coverage convergence and verify multi-threaded processors.

DAC's embedded systems area continues to grow. A panel will determine whether Electronic System-level (ESL) signoff is imminent or impossible. Expect a debate about on-chip communication and it's role in upcoming generations of on-chip systems. Paper presentations will analyze the importance of security, design validation and cache optimization in modern embedded system design.

Emerging technologies that are enabling to the Moore's Law tracjectories of integration and cost - notably die stacking, system in package (SiP) and magnetic RAM - find their place in the "Beyond-the-Die" Track.

On-chip variability remains an important topic, with paper topics spanning improvements in statistical timing analysis, statistical transistor modeling, and methods to calculate on-chip capacitance sensitivity. Methods to avoid crosstalk and power delivery noise and to mitigate the effects of dynamic power gating will also be discussed. A DFM session will address what effects need to be considered during the design phase to minimize post-tapeout issues, and what circuit parameters need to be considered for more effective mask data preparation.

The technical program contains eight topical panels, including one that details how to verify extremely large systems and another that assesses the current state of DFM from the vantage point of practitioners working with cutting-edge technologies. A business-focused panel, (Session 6) goes beyond EDA and electronics design, and addresses how changes in the political and regulatory context can benefit our industry. Yet another panel will review whether custom design offers a worthwhile benefit over synthesized logic, while another panel will look at on-chip thermal problems. A slate of Pavilion panels, held on the exhibit floor, complements the technical program lineup by addressing design methodology, advanced technologies and business, as well as wireless theme-related other new topics.

Finally this year's technical program features six tutorials on subjects that span modern software programming, DFM, system-level synthesis and verification, system-level design for embedded systems, low-power design, and practical mixed-signal design principles. All tutorials have an emphasis on technology fundamentals that can be used productively - and immediately - in the design process. In addition, each tutorial has one or more speakers who are practitioners and use the technology on production designs.

The theme for this year's Hands-on Tutorials (HoTs) is "Embedding Intellectual Property (IP) in your Design: Challenges and Solutions."

# Wireless Theme

Wireless applications can be found in every aspect of our lives. The wireless communications industry is diverse, with its products ranging from systems such as cellular phones, to personal wireless internet such as WiFi, to shorter-range devices such as low-power Bluetooth devices.

DAC explores wireless design and its impact on design automation from both a business and a technical perspective. While wireless communications systems represented more than 67% of the total communications systems market in 2007, cellular technology was more than 40% of that wireless market and remains the dominant driver of design automation technology.

Wireless semiconductor systems design requires design success on numerous fronts. This makes DAC the ideal place for the industry to explore design automation advances to solve wireless design challenges. Across a broad selection of technical paper sessions, special sessions, iDesign track, panels, and Pavilion panels, the DAC program covers the pressing deepsubmicron, complex SoC design, verification, low-power and hardware/software design challenges that must be resolved to enable continued productivity of wireless design teams.

- Monday, June 9 / 10:45 11:45am

Booth #364

PAVILION PANEL: EDA Heritage Series: Maxwell's Legacy

- Monday, June 9 / 3:00 3:45pm

Booth #364

PAVILION PANEL: Today's Consumers: High Schoolers Spec

Your Next Product

- Tuesday, June 10 / 8:30 10:15am Ballroom ABC KEYNOTE: EDA for Digital, Programmable, Multi-radios

- Tuesday, June 10 / 4:00 4:45pm

Booth #364

PAVILION PANEL: Quality Versus Time to Market: The Unmentionable Tradeoff

- Wednesday, June 11 / 9:00 11:00am Room: 208AB PANEL: Next Generation Wireless-multimedia Devices - Who is up for the Challenge?

- Wednesday, June 11 / 11:15am 12:15pm

Ballroom ABC

KEYNOTE: Challenges on Design Complexities for Advanced

Wireless Silicon Systems

- Wednesday, June 11 / 2:00 4:00pm

Room: 208AB

SESSION: Advanced Wireless Design

- Wednesday, June 11 / 3:30 4:30pm

Booth #364

PAVILION PANEL: Designing the New-generation Wireless

Platform: Lessons from iPhone and Android

- Wednesday, June 11 / 4:30 6:00pm Room: 208AB

SPECIAL SESSION: Wireless: Business Meets Technology

DESIGNAUTO MATION CONFERENCE

HALLS: B, C, AND D

**Exhibition Hours:**

Monday - Wednesday, June 9 - 11 / 9:00am - 6:00pm Thursday, June 12 / 9:00am - 1:00pm

Visit the DAC exhibition to learn in-depth information on new products and services from 225 vendors offering products and services for all phases of the electronic design process including EDA tools, IP cores, embedded system and system-level tools, as well as design-for-manufacturing, silicon vendors and design services companies. The DAC show floor features its unique exhibit booth and private suite combination, which gives you the freedom to deeply explore the products on the show floor and find the right solution for your design flow. Visit the DAC exhibition and find out how you can improve performance and shorten the time-to-market on your next design.

### Check out these exciting features of the DAC exhibition:

NEW Best of DAC contest! Look for kiosks on the show floor and vote for your favorite vendors! When you cast your ballot you will be entered to win one of three Nintendo Wiis!

NEW Exhibitor Forum - DAC's newest feature for exhibit floor education. Attendees are invited to the Exhibitor Forum in Booth 2849 to hear a series of technical presentations from exhibitors on focused topics. Compare how exhibitors are solving your tough design issues with their latest tools and methodologies.

DAC Pavilion - The popular DAC Pavilion is back in Booth 364 with 20 presentations this year on business and technical issues.

#### Visit these First-time Participating Companies at DAC:

| ACCIT - New Systems Research<br>Booth 1375   | DTC, National Tsing Hua<br>University<br>Booth 2867 | iNoCs<br>Booth 1478                   | Snowbush Microelectronics<br>Booth 1435            | WinterLogic Inc.<br>Booth 2767        |

|----------------------------------------------|-----------------------------------------------------|---------------------------------------|----------------------------------------------------|---------------------------------------|

| Acresso Software Inc.                        | Duolog Technologies Ltd.                            | Jspeed Design Automation, Inc.        | SOI Consortium                                     | IP, Design Services and Test          |

| Booth 1376                                   | Booth 241                                           | Booth 2866                            | Booth 678                                          | Companies                             |

| Amiq Consulting S.R.L.                       | Electronic Design and Solution                      | Laflin HOTSCOPE                       | Sonnet Software, Inc.                              | Cyclos Semiconductor, Inc.            |

| Booth 682                                    | Fair 2009                                           | Booth 679                             | Booth 2119                                         | Booth 1378                            |

| Axilica Ltd.                                 | Booth 780 eXludus Tech., Inc.                       | Paradigm Works, inc.                  | Spatial                                            | PLD Applications (PLDA)               |

| Booth 1373                                   |                                                     | Booth 2318                            | Booth 421                                          | Booth 1479                            |

| Common Platform                              | Booth 1675 GATelC                                   | Polar Instruments Inc.                | Synapse Design Automation                          | Polar Instruments, Inc.               |

| Booth 628                                    |                                                     | Booth 1379                            | Booth 671                                          | Booth 1379                            |

| Cyclos Semiconductor, Inc.<br>Booth 1378     | Booth 1371  Gauda                                   | POLYTEDA Software Corp.<br>Booth 1365 | Tech Source Media, Inc./<br>SCDSource<br>Booth 606 | SeaSolve Software, Inc.<br>Booth 1673 |

| Dorado Design Automation, Inc.<br>Booth 2660 | Booth 323  Imera Systems, Inc.  Booth 2861          | Satin IP Tech.<br>Booth 1474          | Tela Innovations<br>Booth 473                      |                                       |

|                                              | DUUUI 200 I                                         | SeaSolve Software Inc.<br>Booth 1673  | The RTC Group                                      |                                       |

Booth 2765

# **Tuesday Keynote**

## JUNE 10/8:30 - 10:15AM

RM: BALLROOM ABC

# EDA for Digital, Programmable Multi-radios

**Justin R. Rattner,** Intel Senior Fellow Vice President, Director, Corporate Technology Group and Chief Technology Officer, Intel Corp., Hillsboro, OR

New technology and innovative usage models are driving the industry towards the ubiquitous use of wireless communications. The result is an end-to-end re-examination of radio architecture from the front end module to the MAC and the expected shift from largely analog to nearly pure digital radio design. Even RF power amplifiers will be digital, rather than analog in nature. Most importantly, radios will enter an age where one physical radio acts as many logical radios all at the same time. Much in the way computers evolved decades ago, radios will become multi-programmable. The combination of new radio architectures and mostly digital implementations will drive a new generation of design tools and techniques and, by necessity, will evolve to satisfy the demands of reconfigurable hardware and software programmability. Digital multi-radios will also accelerate the move from System-on-Chip to Platform-on-Chip design as all the elements of the platform, including the radios, are built on one chip using a single semiconductor process.

In his keynote, Intel's Chief Technology Officer, Justin Rattner, will talk about the challenges that this very high level of integration will have on design automation from architecture to manufacturing.

Justin Rattner, 59, is vice president and chief technology officer (CTO). He is also an Intel Senior Fellow and head of the Corporate Technology Group. In the latter role, he directs Intel's global research efforts in microprocessors, systems, and communications including the company's disruptive research activity.

In 1989, Rattner was named Scientist of the Year by R&D Magazine for his leadership in parallel and distributed computer architecture. In December 1996, Rattner was featured as Person of the Week by ABC World News for his visionary work on the Department of Energy ASCI Red System, the first computer to sustain one trillion operations per second (one teraFLOPS) and the fastest computer in the world between 1996 and 2000. In 1997, Rattner was honored as one of the Computing 200, the 200 individuals having the greatest impact on the U.S. computer industry today, and subsequently profiled in the book Wizards and Their Wonders from ACM Press.

Rattner has received two Intel Achievement Awards for his work in high-performance computing and advanced cluster communication architecture. He is a member of the executive committee of Intel's Research Council and serves as the Intel executive sponsor for Cornell University where he is a member of the External Advisory Board for the School of Engineering. Rattner is also a trustee of the Anita Borg Institute for Women and Technology.

Rattner joined Intel in 1973. He was named its first Principal Engineer in 1979 and its fourth Intel Fellow in 1988. Prior to joining Intel, Rattner held positions with Hewlett-Packard Company and Xerox Corporation. He holds B.S. and M.S. degrees from Cornell University in electrical engineering and computer science.

## JUNE 11 / 11:15AM - 12:15 PM

RM: BALLROOM ABC

# Challenges on Design Complexities for Advanced Wireless Silicon Systems

Sanjay K. Jha Chief Operating Officer of Qualcomm, Inc. President of Qualcomm CDMA Tech., San Diego, CA

The global wireless landscape continues to change as demand for 3G technology accelerates. Qualcomm is meeting the challenge with its highly integrated SoC solutions that enable customers worldwide to bring more advanced consumer devices to market faster. Relationships and tight collaboration continue to play an integral role in product development, as it becomes more crucial than ever for partnering companies to tackle complex design issues through synergistic groups such as EDA partners, foundry partners and customers. Technology migration with the right approach is also key as chipset design continues to evolve rapidly, bringing a whole new set of design challenges to semiconductor companies. Jha will elaborate on these present and future trends and reveal how collaborative business models are changing the game in chipset design.

Sanjay K. Jha is chief operating officer of Qualcomm, Inc. and president of Qualcomm CDMA Technologies (QCT). QCT is the world's top wireless chipset provider and largest fabless semiconductor producer.

Jha began his career at Qualcomm in 1994. In 2002, he led the formation of Qualcomm Technologies and Ventures, where he managed both the technology investment portfolio and the new technology group as senior vice president and general manager. He became executive vice president of Qualcomm and president of QCT in 2003, and was promoted to chief operating officer of Qualcomm in 2006. He is also a member of the Qualcomm Ventures advisory committee.

Jha has also served as chairman of the Fabless Semiconductor Association, the voice of the fabless business model and a group with more than 450 corporate members, now known as the Global Semiconductor Alliance (GSA).

Prior to joining Qualcomm, Jha held lead design engineering roles with Brooktree Corporation in San Diego, and GEC Hirst Research Labs in London. He holds a Ph.D. in electronic and electrical engineering from the Univ. of Strathclyde, Scotland and received his Bachelor of Science degree in engineering from the Univ. of Liverpool, England.

# **Thursday Keynote**

## JUNE 12/12:45 - 1:45PM

RM: BALLROOM ABC

# Idea to implementation: A Different Perspective on System Design

Jack Little

President and Co-founder, The MathWorks, Inc., Natick, MA

Today's electronic devices are multi-faceted, software-intensive systems that interact with the real world. These interactions create a new kind of complexity that increases pressure on engineering teams to deliver the right product under shrinking schedules. These multi-disciplinary teams are inhibited by gaps between the different tools and workflows they must use for system concept development, hardware design, and software development. Unless we connect these tools, we'll continue to see missed deadlines and spiraling verification costs.

Emerging EDA and software techniques promise to address some complexity issues such as system-on-chip verification and distributed processing. These important advances are necessary but not sufficient, because system design has become more than silicon and software.

To develop any electronic system, engineers must now characterize the impact of the "next-level system" - the system and environment in which their product must operate. For example, the design of the electronics and software in a hybrid electric vehicle depends on requirements imposed by vehicle dynamics, while a multimedia mobile phone's design is impacted by network traffic.

In response to this challenge, we have seen a significant movement to bridge math-based system modeling with established hardware and software implementation and verification flows using Model-based Design. Central to this approach are multi-domain models that engineers use to specify and validate system behavior. The models provide the basis for design elaboration, automatic code generation, and earlier detection and correction of design flaws.

Leading automotive and aerospace companies have applied model-based design to accelerate embedded system development while improving software reliability, supported by a broad collection of vendors providing simulation, prototyping, implementation, and testing capabilities. Now this approach is rapidly extending into communications, electronics, industrial automation, and other industries as new tools, workflows, and partnerships are established to address design and verification problems that span systems, hardware, and software.

The solution to tomorrow's design challenges won't come solely from any one of the traditional tool categories, but from an interdisciplinary collaboration to deliver a complete tool chain that provides a flow from idea to system implementation. This will provide great value to companies that develop embedded systems and electronics, while creating growth opportunities for all tools that participate in the new workflow.

Jack Little is president and a co-founder of The MathWorks, Inc. He was a co-author and principal architect of early versions of the company's flagship MATLAB product as well as, the Signal Processing Toolbox and the Control System Toolbox.

Little holds a B.S. degree in electrical engineering and computer science from MIT and an M.S.E.E. degree from Stanford University.

A Fellow of the IEEE and Trustee of the Massachusetts Technology Leadership Council, he writes and speaks about technical computing, model-based design, entrepreneurship, and software industry issues.

# **Management Day**

## TUESDAY, JUNE 10 / 8:30AM - 6:00PM

RM: 204BC

Management Day is designed to provide managers with timely information to help them make decisions where business and technology intersect. The day is comprised of three sessions featuring presentations by managers representing key integrated device manufacturers (IDMs) and major fabless companies. Consumer application chips are the technology drivers today. They require different types of optimizations and thus the adoption of emerging solutions to meet such requirements. Optimizing for low power, high volume production, and shrinking sizes necessitates adequate trade-off analysis and technical/business decision making by management. Also, moving to new semiconductor

technology nodes, such as 45nm and 65nm, can significantly affect the choices of suppliers. Management Day sessions will discuss these changing needs and demonstrate corresponding management decision criteria to make the right choices from a pool of alternate options for flows, methodologies and suppliers. The leading managers of today's most complex nanometer chips will present these emerging solutions and their economic impact. This year's Management Day will provide a unique opportunity for managers to gain insights from their peers in the industry.

Registration Required \$95

8:30 - 10:15am Keynote: Justin R. Rattner - EDA for Digital Programmable Multi-radios - Ballroom ABC

10:30am -12:00pm Session 1: Managing Low Power SoC Development on Emerging Technology Nodes

**Session Chair:**

Ron Wilson - EDN Worldwide, San Jose, CA

Session Organizer:

Yervant Zorian - Virage Logic Corp., Fremont, CA

Low power chips are the technology drivers today. They require multi-dimensional optimization and thus the need to adopt emerging technology nodes to meet such requirements. Optimizing for low power production, and shrinking sizes necessitate adequate trade-off analysis and technical/business decision making by management. The leading managers in this session will discuss today's emerging solutions and their economic impact.

Key Design Challenges of 45nm Intel Atom Low Power Processor

**Elinora Yoeli -** Vice President, Mobility Group, Intel Corp., Santa Clara, CA

45/40nm Low Power Design Solutions for Wireless Multi-media SoCs

**Philippe Magarshack -** Vice President, Central R&D, STMicroelectronics, Crolles, France

A Case Study of 65nm 5-million Instances Chip Development

**Andrew C. Chang** - Vice President, Design Tech., MediaTek, Inc., Hsinchu, Taiwan

# **Management Day**

## TUESDAY, JUNE 10 /8:30AM - 6:00PM

км: 204B0

2:00 - 4:00pm Session 2: Trade-offs and Choices for Advanced SoCs in High-volume Application

**Session Chair:**

Nic Mokhoff - EE Times, Manhasset, NY

**Session Organizer:**

**Yervant Zorian** - Virage Logic Corp., Fremont, CA

Design and manufacturing flows and methodologies are directly impacted by the demand for high volume SoCs with increasing performance and parallelism. Moving to new semiconductor technology nodes while producing in high volumes can significantly affect the choices of suppliers. This session will provide an overview of changing needs and corresponding management decision criteria to make the right choices from a pool of alternate options for flows, methodologies and internal/external suppliers.

#### Challenges That New Wireless SoC Designs Are Facing from New Process Technology Nodes

Charles Matar - Vice President of Engineering, Qualcomm, Inc., San Diego, CA

#### A 45nm Power Optimized Digital Baseband SoC - An Introspective Review

**Bob Pitts -** 45nm Platform Manager, Texas Instruments, Inc., Dallas, TX

#### Graphics Processor for XBOX-360 - Cost Reduction - Design Challenges and Decision Criteria

Srinivas Nori - ASIC Design Manager, XBOX Silicon Development, Microsoft Corp., Mountain View, CA

#### From Specifications to High Volume Production

Manuel D'Abreu - Director, SanDisk Corp., Milpitas, CA

#### 4:30 - 5:30pm Session 3: Panel Discussion - Making Critical Decisions for Emerging SoC Development

#### **Session Chair:**

Peggy Aycinena - EDA Confidential, San Mateo, CA

#### Session Organizer:

Yervant Zorian - Virage Logic Corp., Fremont, CA

This panel is designed to provide the attendees with timely information to help them make decisions where business and technology intersect. The panel complements the two management presentation sessions where the key managers of today's most complex nanometer chips will discuss the emerging solutions and discuss their economic impact. This Management Day panel will provide a unique opportunity for all attending managers to interact directly with the panelists and gain insights from their peers in the industry.

#### **Panelists:**

Elinora Yoeli, Vice President, Mobility Group, Intel Corp., Santa Clara, CA

Philippe Magarshack, Vice President, Central R&D, STMicroelectronics, Crolles, France

Andrew C. Chang, Vice President, Design Tech., MediaTek, Inc., Hsinchu, Taiwan

Charles Matar, Vice President of Engineering, Qualcomm, Inc., San Diego, CA

Bob Pitts, 45nm Platform Manager, Texas Instruments, Inc., Dallas, TX

Srinivas Nori, ASIC Design Manager, XBOX Silicon Development, Microsoft Corp., Mountain View, CA

Manuel D'Abreu, Director, SanDisk Corp., Milpitas, CA

5:30 - 6:00pm Reception

# **NEW! Exhibitor Forum - Exhibit Hall D, Booth #2849**

15 min. of 0 & A

# COFLUENT DESIGN - EARLY DECISION TRADE-OFF, ADDRESSING PERFORMANCE CONCERNS IN FUTURE NETWORK INFRASTRUCTURE

#### Monday, June 9 / 9:30 - 10:10am

As demand on network resources grows, and multi-core processing capabilities increase, software elements are soon to dominate the networking infrastructure application domain. System architects have to make correct cost-impacting decisions and performance tradeoffs, prior to any implementation commitment or development investment. Following a "Y" design flow, CoFluent Studio allows users to elaborate the most adequate partitioning strategy across multiple cores, distributing I/O connectivity, managing shared resources, optimizing communications on the fabric interconnect and profiling power consumption.

Presenters: Hagay Zamir, Laurent Isenegger - CoFluent Design, San Jose, CA

# MENTOR GRAPHICS CORP. - OBJECT ORIENTED HARDWARE REUSE WITH ANSI C+++ AND ALGORITHMIC SYNTHESIS

#### Monday, June 9 / 10:10 - 10:50am

Both algorithm researchers and hardware designers can learn how to use ANSI C+++ to implement and verify algorithmic designs in ASIC or FPGA hardware, balancing design requirements for performance, area and power with Algorithmic C Synthesis. This exhibit will cover a coding style based on C+++ object oriented templates for a highly flexible reuse methodology. The end result is high performance hardware typical in wireless, video and imaging products.

Presenter: Andres Takach - Mentor Graphics Corp., Wilsonville, OR

# MENTOR GRAPHICS CORP. - WHAT YOU SHOULD KNOW ABOUT THE OPEN VERIFICATION METHODOLOGY (OVM)

#### Monday, June 9 / 10:50 - 11:30am

This presentation covers the use and benefits of the Open Verification Methodology (OVM). The OVM brings together verification knowledge, experience and expertise to provide a modular approach to building reusable verification IP and testbenches powerful enough to meet the most demanding requirements, yet easy to adopt. We will touch on all aspects of the OVM, including the following: testbench architecture, transaction-level modeling in verification, sequential stimulus and block-to-system-level reuse.

Presenter: Tom Fitzpatrick - Mentor Graphics Corp., Wilsonville, OR

# MAGMA DESIGN AUTOMATION - TITAN™ CHIP FINISHING AND FASTER ANALOG DESIGN IMPLEMENTATION/MIGRATION

#### Monday, June 9 / 2:00 - 2:40pm

Efficiency improvements in analog design implementation/migration have not kept pace with the digital standard cell world. In addition, finishing complex mixed-signal chips has become increasingly unwieldy due to the database and tool disconnect between the analog and digital domains. Titan, the comprehensive mixed-signal platform from Magma, addresses both these areas by bringing unprecedented automation to analog circuit design, optimization, floorplanning, placement and routing. Titan eliminates the disconnect between the analog and digital domains in handling late ECOs, verification and custom layout for chip finishing.

**Presenter: Khalid Islam -** Magma Design Automation, Inc., Austin, TX

# MENTOR GRAPHICS CORP. - MENTOR GRAPHICS CORP. AND AGILENT TECHNOLOGIES INTEGRATED RF DESIGN SOLUTION FOR PCBs

#### Monday, June 9 / 2:40 - 3:20pm

The proliferation of wireless consumer devices has pushed the PCB design envelope, due to increasingly short time-to-market windows for innovative products that require greater functionality. Mentor's new RF Design Solution allows simultaneous and seamless RF, analog, and digital design in Expedition Enterprise and Agilent ADS through Mentor's two-way Dynamic Link interface. This integration of technologies allows full parameter-driven schematic and layout design with an easily-synchronized RF library, providing the most automated mixed-signal design, simulation, and implementation solution on the market.

Presenters: John Isaac, Per Viklund - Mentor Graphics Corp., Longmont, CO

Free and open to ALL attendees!

# **NEW! Exhibitor Forum - Exhibit Hall D, Booth #2849**

## DENALI SOFTWARE, INC. - KEY INGREDIENTS OF A NEXT-GENERATION NAND FLASH PLATFORM

#### Monday, June 9 / 3:20 - 4:00pm

This presentation will discuss the challenges of developing and verifying a multichannel NAND Flash SoC platform Flashpoint™; which was designed to maximize the random read/write operations of the controller and maximize the bandwidth of a system using NVMHCI, PCIe 2.0, and ONFi 2.0. We will explore several key developments and tools that allow Flashpoint to achieve the desired performance parameters, including HW–SW partitioning and extensive use of DMA and hardware accelerated approaches.

Presenter: Robert Pierce - Denali Software, Inc., Sunnyvale, CA

This session followed by 15 min. of 0 & A

## MENTOR GRAPHICS CORP. - 2-D AND 3-D VARIABILITY OPTIMIZATION

#### Tuesday, June 10 / 2:00 - 2:40pm

Variability is a reality creating hurdles in physical design and verification. To ease designers' jobs, DFM must be integrated into design flows to automate improvements, manage complex design rules, and ensure timing closure based on "as built" device and interconnect models. This session shows designers how to deal with variability and reduce time to tapeout; how DFM tools are expanding from 2-D to 3-D analysis and from functional to electrical DFM; how DFM can be integrated into the design process.

Presenter: David Abercrombie - Mentor Graphics Corp., Wilsonville, OR

# MENTOR GRAPHICS CORP. - MULTI-CORNER-MULTI-MODE P&R FOR TIMING, POWER, AND SI CLOSURE

#### Tuesday, June 10 / 2:40 - 3:20pm

Achieving closure for ICs with many operating modes and complex low power techniques is a critical design challenge in advanced ICs. Smaller geometries present more difficult signal integrity problems; higher interconnect resistance impacts circuit performance and reliability of clock trees. Designs are taking longer and designers are forced to increase design margins, leaving performance on the table. This session shows how multi-corner-multi-mode timing and SI analysis and DFM-aware routing can improve the speed and quality of advanced 45nm designs.

Presenter: Sudhakar Jilla - Mentor Graphics Corp., San Jose, CA

# BLAZE DFM, INC. - LEAKAGE POWER REDUCTION USING ELECTRICAL DFM TECHNIQUES (CUSTOMER CASE STUDY)

#### Tuesday, June 10 / 3:20 - 4:00pm

Blaze MO reduces leakage power by 20% and cuts leakage variability in half on 90nm, 65nm, and 45nm digital chips. It has been proven in silicon on numerous customer designs. It works on both new and existing designs. It does not require changes to the chip architecture, IP blocks, libraries, logic design, or layout. A customer case study will be presented on how the design team was able to significantly lower leakage power on a multi-million gate system-on-chip (SoC).

<u>Presenter:</u> Dave Reed - Blaze DFM, Inc., Sunnyvale, CA

## PYXIS TECHNOLOGY, INC. - PYXIS HIGH PERFORMANCE YIELD-AWARE IC ROUTER

#### Wednesday, June 11 / 9:15 - 9:55am

Pyxis Technology will give a presentation on its NexusRoute IC router, highlighting key architectural features required for 45nm design closure and contrasting these features against existing router architectures. The presentation will also discuss how the router has been successfully integrated into existing EDA design flows and used with customers such as Microsoft Corporation to provide as much as a 4X improvement in design closure cycle time with faster circuit performance, lower power and higher predicted yield.

**Presenter: Phil Bishop -** Pyxis Tech., Inc., Austin, TX

This session followed by 15 min. of Q & A

# **NEW! Exhibitor Forum - Exhibit Hall D, Booth #2849**

TEKLATECH - IR DROP AND NOISE AWARE SOC FLOORPLANNING

#### Wednesday, June 11 / 9:55 - 10:35am

As IC fabrication technologies scale into nanometer geometries, physical-level issues present an increasing challenge to semiconductor companies. Addressing power and timing integrity in early design phases is critical to maintaining proper sign-off without compromising leakage power, area and design time. Increasing parasitics and fast on-chip switching times make it vital to control the dynamic power usage in order to reduce noise and IR drop peaks. Teklatech's FloorDirector™ provides IR drop and noise aware floorplanning, enabling designs which are robust to sign-off challenges.

Presenter: Tobias Bjerregaard - Teklatech, Copenhagen, Denmark

## TELA INNOVATIONS, INC.- 45nm LEAKAGE REDUCTION USING GRIDDED, ONE DIMENSIONAL LAYOUT

#### Wednesday, June 11 / 10:35 - 11:15am

45nm test chip results will be presented based on Tela Innovations proprietary, unidirectional, on-grid layout techniques demonstrating substantial reduction in leakage, variability and area. Tela's topology based layout methodology will be reviewed in the context of existing SoC design flows. The applicability of these layout structures to enable double patterning techniques for 32nm and 22nm nodes will be covered.

Presenter: Neal Carney - Tela Innovations, Inc., Campbell, CA

This session followed by 15 min. of Q & A

## AZURO, INC. - CLOCK IMPLEMENTATION FOR NANOMETER CHIP DESIGN

#### Wednesday, June 11 / 2:00 - 2:40pm

Effective clock design at nanometer geometries requires some new thinking to keep CTS from becoming a major bottleneck in the flow. A CTS tool must be directly driven by the designer's underlying objectives, such as timing, power, and area. Customers are using Azuro's PowerCentric in all major design flows as a complete CTS solution, addressing dynamic power, skew, insertion delay, OCV, variability and routability. PowerCentric also provides unique visualizations that permit designers to manage even the most complex clock structures.

Presenter: Marc Swinnen - Azuro, Inc., Santa Clara, CA

# SYNFORA, INC. - ARCHITECTURAL EXPLORATION FOR LOW POWER DESIGN USING PICO EXTREME

#### Wednesday, June 11 / 2:40 - 3:20pm

Power consumption, rather than area, is an increasingly key design parameter for SoCs for integrated mobile devices. Currently, designers have no practical method to perform architectural and micro-architectural exploration for low power design. Algorithmic synthesis using PICO Extreme enables the implementation of complex hardware sub-systems from untimed, sequential C algorithms. Integration of PICO Extreme with an RTL power estimation tool enables exploration of multiple algorithms and architectures with different power profiles to determine the optimal algorithm-architecture combination in a very short period of time. This presentation will describe this new methodology for low power design and illustrate it using real-life examples.

Presenter: Vinod Kathail -Synfora, Inc., Mountain View, CA

## SEQUENCE DESIGN, INC. - DESIGN FOR POWER

#### Wednesday, June 11 / 3:20 - 4:00pm

Design for Power (DFP) has become essential for product success, especially in today's consumer driven battery powered market. This presentation will focus upon particular DFP methods and techniques, focusing on those deployed early in the design process when DFP can be most effective. In addition, the concept of power regression testing will be introduced as a means of tracking and controlling power consumption beginning at the earliest design phases and continuing through tapeout.

Presenter: Jerry Frenkil - Sequence Design, Inc., Santa Clara, CA

15 min. of Q & A

# MONDAY, JUNE 9/9:30 - 10:30AM

#### PAVILION PANEL: GARY SMITH ON EDA: TRENDS AND WHAT'S HOT AT DAC

Chair: Robert Gardner - EDA Consortium, San Jose, CA

Organizer: Gary Smith - Gary Smith EDA, Santa Clara, CA

EDAC brings you DAC's traditional kick off: Gary Smith reviews EDA's hottest technology trends. What's shaping design over the next 5 years? How is DFM changing EDA? How is parallel computing affecting EDA tool development? Which acquisitions were critical in 2007 and which ones should you watch for in 2008? What are the "must see" products? Find out here!

#### Speaker:

Gary Smith - Gary Smith EDA, Santa Clara, CA

## MONDAY, JUNE 9 / 10:45 - 11:45AM

#### PAVILION PANEL: EDA HERITAGE SERIES: MAXWELL'S LEGACY

Chair: Rich Goldman - Synopsys, Inc., Mountain View, CA Organizer: Rich Goldman - Synopsys, Inc., Mountain View, CA

James Clerk Maxwell stands shoulder to shoulder with Newton and Einstein, yet even those of us who have spent decades working with Maxwell's equations are almost totally unfamiliar with his life and times. What is Maxwell's legacy to us? This presentation provides insight into Maxwell's life and adds depth to those four simple equations we have studied ever since.

#### Speaker:

James C. Rautio - Sonnet Software, Inc., Syracuse, NY

## MONDAY, JUNE 9 / 2:00 - 2:45PM

#### PAVILION PANEL: NEXT GENERATION DATA CENTERS: ENVIRONMENTALLY GREEN. FINANCIALLY GREEN

Chair: Joel Swisher - Rocky Mountain Institute, Boulder, CO

Organizer: Kevin Silver - Denali Software, Inc., Palo Alto, CA

Data center energy costs can be 100 times higher than those for typical buildings according to Lawrence Berkeley National Laboratory. Even a small improvement in energy efficiency can significantly reduce environmental impact and operating costs. Following an overview of data centers and the challenges associated with energy efficiency, the panelists take a fresh look at leading-edge technology and environmental legislation that enable green data centers.

#### Speakers:

Dileep Bhandarkar - Microsoft Corp., Redmond, WA Mark Bramfitt - PG&E Corp., San Francisco, CA Bill Weihl - Google, Washington, DC

## MONDAY, JUNE 9 / 3:00 - 3:45PM

#### PAVILION PANEL: TODAY'S CONSUMERS: HIGH SCHOOLERS SPEC YOUR NEXT **PRODUCT**

Chair: Kathryn Kranen - Jasper Design Automation, Inc., Mountain View, CA Organizer: Rich Goldman - Synopsys, Inc., Mountain View, CA

We all want to design the new hot consumer device like the iPod or the Wii. Today's consumers are college students and high schoolers, and they think very differently from you. This panel features tech savvy Java programming students. Hear what these high schoolers find cool in current devices and what they want in the future.

#### Speakers:

JonMichael Guay, Brett Davis, Justin Towers - Servite High School, Anaheim, CA

## MONDAY, JUNE 9 / 12:00 - 1:00PM

#### PAVILION PANEL: STUDENT DESIGN CONTEST AWARD PRESENTATION

**Chair: Byunghoo Jung** - *Purdue Univ., West Lafayette, IN* Organizer: William Bowhill - Intel Corp., Hudson, MA

Presentation of the nine student design award winners, across operational, system-level and conceptual award categories of the Student Design Contest, organized by the Design Automation Conference and the International Solid-state Circuits Conference (ISSCC).

## MONDAY, JUNE 9 / 4:00 - 5:00PM

#### PAVILION PANEL: WILL 22NM BE OUR CATCH-22?

Chair: Joe Sawicki - Mentor Graphics Corp., Wilsonville, OR **Organizer: Gene Forte** - Mentor Graphics Corp., Wilsonville, OR

Does the world end at 22nm? Will optical lithography fail, forcing us to use nanoimprinting, direct-write e-beam or some other exotic imaging technology? Will silicon fail us completely? This panel of experts drawn from the tools, design services, process technology, and semiconductor foundry communities looks into their collective crystal ball for answers.

#### Speakers:

**S. T. Juang -** Taiwan Semiconductor Manufacturina Company, Ltd., Hsin-Chu,

John Kibarian - PDF Solutions, Inc., San Jose, CA Lars Liebmann - IBM Corp., East Fishkill, NY

# TUESDAY, JUNE 10 / 10:30 - 11:15AM

#### PAVILION PANEL: 45nm: COLLABORATE, AGGREGATE, DIFFERENTIATE

Chair: Mike Santarini - Xilinx, Inc., San Jose, CA

Organizer: Phil Dworsky - Synopsys, Inc., Mountain View, CA

At 45nm, process is being defined by a limited few, everyone has access to the same IP and tools, and fabs may no longer be differentiators even for IDMs. Where will differentiation come from? Some companies are turning to collaboration; others are moving toward a reaggregated model. These experts will explore how companies can succeed at 45nm and beyond.

Speakers:

Naveed Sherwani - Open-Silicon, Inc., Milpitas, CA

Ana Hunter - Samsung, San Jose, CA

Alex Shubat - Virage Logic Corp., Fremont, CA

# TUESDAY, JUNE 10/2:00 - 2:45PM

#### PAVILION PANEL: IP SELECTION: THE GOOD, THE BAD, AND THE UGLY

Chair: Jordan Selburn - iSuppli Corp., El Segundo, CA

Organizer: Meghan Le - Synopsys, Inc., Mountain View, CA

As the number of third-party IP vendors increases, the quality of available IP varies dramatically. Although purchased IP can reduce project cycle time and improve time to market, integrating a bad (or worse, ugly) piece of IP can mean costly re-spins and missed market windows. How do you find the gold among the dross?

#### **Speakers:**

Satya Gupta - Open-Silicon, Inc., Milpitas, CA Joachim Kunkel - Synopsys, Inc., Mountain View, CA Kathy Werner - Freescale Semiconductor. Inc., Austin. TX

## TUESDAY, JUNE 10 / 11:30AM - 12:15PM

#### PAVILION PANEL: EDA: A VIEW FROM SAND HILL ROAD

<u>Chair:</u> <u>Lucio Lanza</u> - *Lanza Tech. Ventures, Palo Alto, CA*<u>Organizer:</u> <u>Dave Kelf</u> - *Sigmatix, Inc., Boston, MA*

Today, locating investment for even the most exciting of EDA startups is challenging. What are investors looking for in EDA companies, what are the interesting trends and opportunities and what investments are being made? Why is investment in EDA critical to the entire electronics industry?

#### **Speakers:**

Juan-Antonio Carballo - Argon Venture Partners, Redwood City, CA Kent Shimasaki - Nollenburger Partners, San Francisco, CA Erach Desai - Integrated Corporate Relations, Inc, Boston, MA

## TUESDAY, JUNE 10/3:00 - 3:45PM

#### PAVILION PANEL: EDA GLOBALIZATION: THIRD WORLD OR NEW WORLD?

<u>Chair:</u> Jodi Shelton - Global Semiconductor Alliance, Dallas, TX Organizer: Yatin Trivedi - Magma Design Automation, Inc., San Jose, CA

Leading edge SoC projects are now starting in far away places. EDA suppliers must support them as if in their own backyards. What are the challenges? Has outsourcing encircled the EDA industry or does EDA have it covered? Semiconductor industry leaders from India and China present the everyday challenges and unique solutions offered by the local industry ecosystems.

#### Speakers:

S. Janakiraman - Mindtree Services, Bangalore, India Shaojun Wei - Tsinghua Univ., Beijing, China

## TUESDAY, JUNE 10/1:00 - 1:45PM

#### PAVILION PANEL: MULTI-PROCESSOR SoCs: THE NEXT GENERATION

<u>Chair: Markus Levy - Multicore Assoc., El Dorado Hills, CA</u> <u>Organizer: Dave Kelf - Sigmatix, Inc., Boston, MA</u>

A 1990s IC designer awakening from a coma in 2008 would observe little change in the SoC design/verification flows, despite order of magnitude leaps in multiprocessor SoC complexity. Recent ESL advances, such as transaction-based acceleration/emulation, system-level modeling, virtual prototyping, platform-based design, and high level synthesis have not yet gone mainstream. Why not?

#### Speakers:

Sreenivasa Rao - Analog Devices, Inc., Wilmington, MA Laurent Ducousso - STMicroelectronics, Grenoble, France Grant Martin - Tensilica, Inc., Santa Clara, CA

## TUESDAY, JUNE 10 / 4:00 - 4:45 PM

# PAVILION PANEL: QUALITY VERSUS TIME TO MARKET: THE UNMENTIONABLE TRADEOFF

Chair: Will Strauss - Forward Concepts Co., Tempe, AZ

Organizer: Rajiv Maheshwary - Synopsys, Inc., Mountain View, CA

The enormous wireless market has completely altered the rules of product development. Timeliness is everything. But does timeliness come at the expense of quality and performance? This panel will explore how to improve turn around time (TAT), time to results (TTR), and time to market (TTM), but would you trade off quality for a 50% increase in these areas?

#### **Speakers:**

Andrew C. Chang - MediaTek, Inc., Hsinchu, Taiwan Atul Jain - Texas Instruments, Inc., Bangalore, India T. W. Williams - Synopsys, Inc., Mountain View, CA

## TUESDAY, JUNE 10 / 5:00 - 5:45PM

#### PAVILION PANEL: SOI: FACT, FUTURE AND FICTION

Chair: Richard Goering - SCDsource, Felton, CA

Organizer: Horacio Mendez - SOI Industry Consortium, Austin, TX

Silicon on Insulator (SOI) technology has promised a next-generation alternative to traditional bulk CMOS, enabling high performance without the heat and power issues associated with other substrates. Although SOI has been perceived as cost-prohibitive for all but limited applications, recent developments demonstrate otherwise. This panel of SOI experts will discuss the benefits and challenges associated with SOI.

**Speakers:**

Percy Gilbert - IBM Corp., East Fishkill, NY

Nick Kepler - Advanced Micro Devices, Inc., Sunnyvale, CA

Jean-Luc Pelloie - ARM, Grenoble, France

## WEDNESDAY, JUNE 11 / 2:30 - 3:15PM

#### **PAVILION PANEL: DFM DESIGN RULES: WORTH THE EFFORT?**

Chair: Dave Maliniak - Electronic Design, Penton Media, New York, NY

Organizer: Cedric Iwashina - Blaze DFM. Inc., Sunnyvale, CA

At 65nm, foundries have added many new design rules intended to improve manufacturability and boost yield. But are these rules working for you? If so, do the benefits justify the increased cost and complexity of design? How many more rules will you have to endure in the future and how many will remain optional?

**Speakers:**

Michael Buehler-Garcia - Ponte Solutions, Inc., Mountain View, CA

**Ed Chen** - Advanced Micro Devices, Inc., Sunnyvale, CA

Walter Ng - Chartered Semiconductor Manufacturing, Milpitas, CA

## WEDNESDAY, JUNE 11 / 9:30 - 10:30AM

#### PAVILION PANEL: HOGAN'S HEROES - BEHAVIORAL SYNTHESIS: IS THAT LIGHT AT THE END OF THE TUNNEL AN ONCOMING TRAIN?

<u>Chair:</u> Jim Hogan - Vista Ventures Partners, Campbell, CA <u>Organizer:</u> Jim Hogan - Vista Ventures Partners, Campbell, CA

Jim Hogan grills industry experts about critical system design challenges. What really can be expected of high-level synthesis? Where does h synthesis work? Has a usable methodology and flow developed? What level of abstraction is practical? What types of efficiencies can you expect on first pass and re-spins?

Speakers:

Jason Cong - Univ. of California, Los Angeles, CA Loic Le Toumelin - Texas Instruments, Inc., Nice, France Jan Willis - Calibra, Bracknell, United Kinadom

## WEDNESDAY, JUNE 11 / 3:30 - 4:30PM

# PAVILION PANEL: DESIGNING THE NEW-GENERATION WIRELESS PLATFORM: LESSONS FROM IPHONE AND ANDROID

<u>Chair:</u> Ron Wilson - EDN Worldwide, San Jose, CA <u>Organizer:</u> Dave Kelf - Sigmatix, Inc., Boston, MA

Apple's iPhone has been hailed as a shining example of next-generation user interface design coupled with state-of-the-art wireless technology. Google's proposed Android open software platform is meant to unify applications across different hardware platforms. Portelligent and ARM take you under the covers of these remarkable devices, providing insight on their design advances and innovations.

**Speakers:**

James Bruce - ARM, Sunnyvale, CA

Dave Carey - Portelligent, Inc., Austin, TX

## WEDNESDAY, JUNE 11 / 1:00 - 2:00PM

# PAVILION PANEL: ADVANCED LOW POWER TECHNIQUES: IS YOUR DESIGN METHOD TOO POWERFUL?

Chair: Gary Delp - LSI Logic Corp., Rochester, MN

Organizers: Sabina Burns - Virage Logic Corp., Fremont, CA

Because of the increasing adoption of mobile device technologies and the shift toward sub-90nm geometries, advanced techniques for low power are rapidly moving from early-adopter to mainstream. Panelists will discuss actual experiences "the good and the bad" in applying advanced 65nm and 45nm low power technologies and methodologies in real projects.

Speakers:

Yoshio Inoue - Renesas Tech. Corp., Itami-shi, Hyogo, Japan Juergen Karmann - Infineon Tech. AG, Munich, Germany David Hathaway - IBM Corp., Essex Junction, VT

## WEDNESDAY, JUNE 11 / 5:00 - 5:45PM

#### PAVILION PANEL: WHAT'S HOLDING BACK ANALOG DESIGN AUTOMATION?

Chair: Gabe Moretti - Gabe on EDA, Venice, FL

**Organizer: Dave Millman** - Ciranova, Inc., Santa Clara, CA

While digital design automation has moved forward with amazing speed over the past 20 years, analog design automation has lagged far behind, particularly analog physical design automation. Are analog designers ready for automation? Are adequate analog tools and mother than the past 20 years and 20 years

#### Speakers:

**Anirudh Devgan -** *Magma Design Automation, Inc., Austin, TX*

Jim Solomon - Ciranova, Inc., Santa Clara, CA

Rudy C. Hernandez - Texas Instruments, Inc., Dallas, TX

## THURSDAY, JUNE 12 / 10:00 - 10:45AM

## PAVILION PANEL: NEGOTIATING A SUCCESSFUL CAREER

<u>Chair:</u> Peggy Aycinena - EDA Confidential, San Mateo, CA <u>Organizer:</u> Sabina Burns - Virage Logic Corp., Fremont, CA

Join Intel's Limor Fix, 2008 DAC General Chair, in a one-on-one conversation with EDA Confidential's Peggy Aycinena as they discuss the other side of your career equation — those negotiation and networking skills that can prove as important to your future success as the technical skillset you bring to the workplace. Fix and Aycinena will discuss the challenges of setting short-term and long-term goals, having the wisdom to see your own strengths and weaknesses and how to leverage that wisdom in crafting your career, and the importance of building trusted relationships with your co-workers — particularly in large, distributed, multi-national organizations. Finally, who better than the DAC General Chair to examine the many benefits of attending conferences, the ultimate networking venue. The conversation promises to be lively and wide-ranging, with ample opportunity for audience participation in a discussion that spans both gender and generational issues.

#### **Moderator:**

**Peggy Aycinena -** *EDA Confidential, San Mateo, CA* 2008 Chair, Workshop for Women in Design Automation

#### Speaker:

**Limor Fix -** Intel Research Pittsburgh, Pittsburgh, PA

#### This year's winner of the Marie R. Pistilli Women in EDA Achievement Award:

**Louise Trevillyan** - Research Staff Member, Design Automation Department, IBM T.J. Watson Research Center

## THURSDAY, JUNE 12 / 11:00 - 11:45AM

# PAVILION PANEL: YOUR FUNCTIONAL VERIFICATION ROADMAP: OVM, VMM, OR ROLL YOUR OWN?

Chair: Brian Bailey - Brian Bailey Consulting, Beaverton, OR

Organizer: Francine Bacchini - Francine Bacchini, Inc., San Jose, CA

What is the future for verification? This panel of verification experts will discuss two key verification methodologies, OVM and VMM, and the roadmap for these flows. Learn how and why industry-leading companies have either customized these flows or developed their own methodologies.

#### **Speakers:**

Janick Bergeron - Synopsys, Inc., Mountain View, CA Faisal Haque - Qualcomm, Inc., San Jose, CA Tom Fitzpatrick - Mentor Graphics Corp., Groton, MA

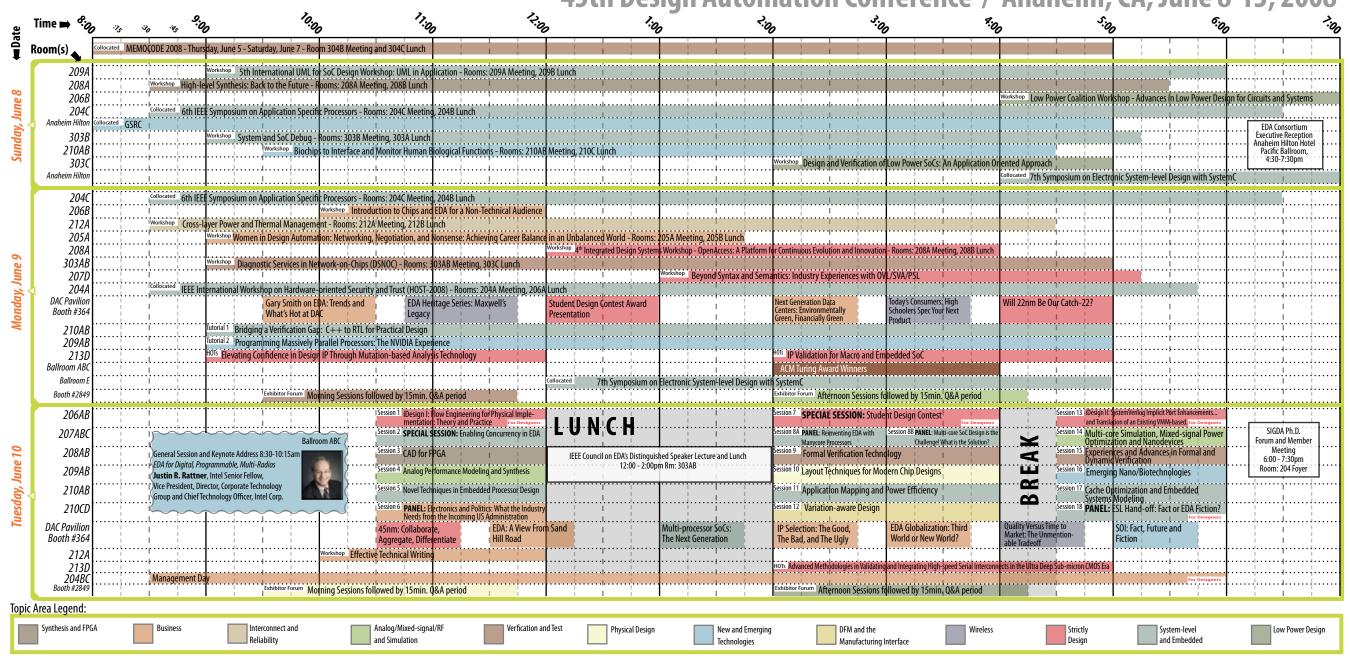

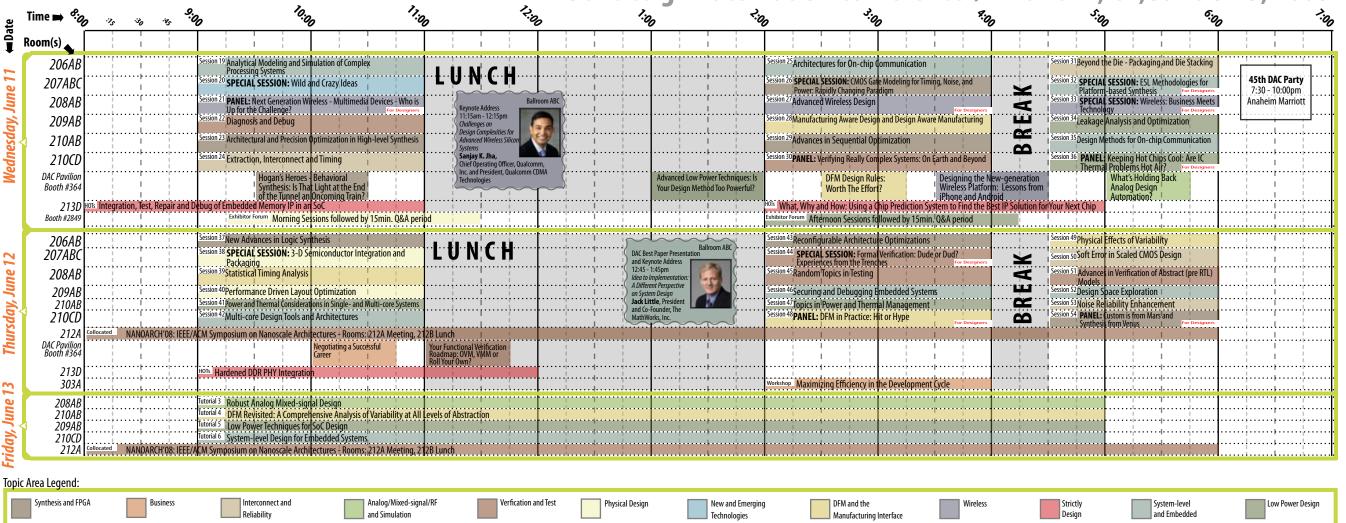

# 45th Design Automation Conference / Anaheim, CA, June 8-13, 2008

# 45th Design Automation Conference / Anaheim, CA, June 8-13, 2008

# **General Session/Keynote Address**

# TUESDAY, JUNE 10/8:30 - 10:15AM

RM: BALLROOM ABC

### Opening Remarks - Limor Fix - 45th DAC General Chair

#### Awards/Scholarships

- A. Richard Newton Graduate Scholarships

- Marie R. Pistilli Women in EDA Achievement Award

- P.O. Pistilli Undergraduate Scholarships for Advancement in Computer Science and Electrical Engineering

- 2007 Phil Kaufman Award for Distinguished Contributions to EDA

- 2008 IEEE Emanuel R. Piore Award

- 2008 IEEE Fellow

- ACM Turing Award

- ACM Fellow

- Outstanding Contribution to ACM Award

- SIGDA Distinguished Service Award

- SIGDA Outstanding New Faculty Award

- ACM Transactions on Design Automation of Electronic Systems (TODAES) 2008 Best Paper Award

### **Keynote Address**

EDA for Digital, Programmable, Multi-radios

Justin R. Rattner - Intel Senior Fellow, Vice President, Director, Corporate Technology Group and Chief Technology Officer, Intel Corp., Hillsboro, OR

# Tuesday, June 10

# 10:30am -12:00pm

SESSION 1

FOR DESIGNERS

rm: 206AB **SESSION 2**

rm: 207ABC **SESSION 3**

rm: 208AB

#### iDESIGN I

Chair:

David Reda - Synopsys, Inc., Irvine, CA Organizer:

**Leon Stok** - IBM Corp., Hopewell Junction, NY

EDA tools are never used in isolation. Rather, multiple tools an elaborate infrastructure is required to support and enable flow execution. This "flow infrastructure" includes directory and the flows themselves.

#### 1.1 Flow Engineering for Physical Implementation: Theory and Practice

Steve Golson - Trilobyte Systems, Carlisle, MA Pete Churchill - EdgeRate Consulting, Hillsborough, NC

#### SPECIAL SESSION: ENABLING CONCURRENCY IN EDA

Chair:

Patrick Madden - Binghamton Univ., NY Organizer:

**Eli Chiprout** - Intel Corp., Hillsboro, OR

desktop machines, job control, license administration, size of our designs and with higher demand for faster results by incrementally updating slack and criticality. dependency management, operating systems, team turnaround time there is also a demand-side motivation for 3.1 Functionally Linear Decomposition and Synthesis communication, error reporting, and libraries of all sorts. enabling EDA to take advantage of multi-core and parallel Oh, and of course the EDA tools themselves. While EDA tools processing. This session will give some fresh perspective on Tomasz S. Czajkowski, Stephen D. Brown - Univ. of come with documentation and user quides, and many of how EDA should be thinking about the problem. The first Toronto, Toronto, Toronto, ON, Canada the components of the flow infrastructure have standalone talk will address new parallel mechanism that are enabled documentation, there is virtually no manual or reference guide for GPUs and an example application on sparse matrices. The 3.2 FPGA Area Reduction by Multi-output Function or checklist available to aid in the creation and improvement second talk will discuss what has been learned in parallel of a flow. Join two veteran consultants, each with over 20 years computing and what is being enabled in multi-core systems Yu Hu, Victor Shih, Rupak Majumdar, Lei He - Univ. experience in IC design, as we discuss the theory and practice to address past mistakes. The third talk will prepare us for the of "flow engineering", the design of "flow infrastructure radical changes that are coming to CAD due to the availability of multi-core systems.

#### 2.1 Sparse Matrix Computation on Manycore GPUs Michael Garland - NVIDIA Corp., Urbana-Champaign, Urbana, IL

#### 2.2 Parallel Computing Technology: Can We PLEASE Do It Right This Time?

Michael Wrinn - Intel Corp., Hillsboro, OR Timothy Mattson - Intel Corp., Dupont, WA

#### 2.3 Parallelizing CAD: A Timely Research Agenda for EDA

Kurt Keutzer, Bryan Catanzaro,

Bor-Yiing Su - Univ. of California, Berkeley, CA

#### CAD FOR FPGA

Chair:

**Yegna Parasuram -** *Mentor Graphics Corp.*, San Jose, CA

This session presents advances in CAD for FPGAs. The first paper presents a novel approach to synthesis of XOR-based are combined into a sequence called a "flow". Furthermore The effort to parallelize applications has been a difficult logic. The second paper reduces netlist area by using multiproblem for many years. However, new directions in output function based sequential resynthesis. The third paper hardware, compiler technology, and software methods have uses a network flow model to minimize power in embedded organization, configuration management, compute servers, forced us to take a new look at the problem. With increasing memory mapping. The final paper improves VPR's timing

# of Logic Circuits for FPGAs

# **Based Sequential Resynthesis**

of California, Los Anaeles, CA

#### 3.3s A Generalized Network Flow Based Algorithm for **Power-aware FPGA Memory Mapping**

Tien-Yuan Hsu, Ting-Chi Wang - National Tsing Hua Univ., Hsinchu, Taiwan

#### 3.4s Enhancing Timing-driven FPGA Placement for **Pipelined Netlists**

Ken Eguro, Scott Hauck - Univ. of Washington, Seattle, WA

# Tuesday, June 10

# 10:30am -12:00pm

DESIGN**AUTOMATION** CONFERENC

rm: 210AB **SESSION** 6 SESSION 4 RM: 209AB **SESSION 5** rm: 210CD

#### ANALOG PERFORMANCE MODELING AND SYNTHESIS

#### Chair:

**Peng Li** - Texas A&M Univ., College Station, TX

constraints simultaneously.

4.1 Statistical Regression for Efficient High-dimensional Modeling of Analog and **Mixed-signal Performance Variations**

**Xin Li** - Carnegie Mellon Univ., Pittsburgh, PA Hongzhou Liu - Cadence Design Systems, Inc., Pittsburah, PA

4.2 Topology Synthesis of Analog Circuits Based on Adaptively Generated Building Blocks

Angan Das, Ranga Vemuri - Univ. of Cincinnati, Cincinnati, OH

#### 4.3 Analog Placement Based on Hierarchical **Module Clustering**

Po-Hung Lin - National Taiwan Univ., Taipei, Taiwan **Shyh-Chang Lin -** *SpringSoft, Inc., Hsinchu, Taiwan*

#### NOVEL TECHNIOUES IN EMBEDDED PROCESSOR DESIGN

#### Chair:

Pai Chou - Univ. of California, Irvine, CA

The first paper in the session presents an innovative response. This session presents advanced topics for the design of surface modeling technique that is very efficient when the highly-optimized embedded processors. The first paper dimension of the parameter space is very large. The second presents a new concept that is capable of dynamically paper presents an analog topology synthesis methodology transmuting its instruction set for an application specific based on a genetic programming formulation that does reconfigurable processor. The second paper presents a novel It's election time again and the US is about to see a new not require an initial building block library and produces algorithm to optimize an application specific floating-point designer-recognizable circuit topologies. The third paper is unit by sharing floating point datapaths with variable biton a placement methodology for analog circuits that takes widths. The third paper presents an adaptive resource resizing into account hierarchical matching, symmetry and proximity scheme that can improve processing performance and energy efficiency simultaneously. The last paper presents an architecture design example of a VoIP codec using a C-based

#### 5.1 Run-time Instruction Set Selection in a Transmutable Embedded Processor

Lars Bauer, Muhammad Shafique, Jörg Henkel - Univ. of Karlsruhe, Karlsruhe, Germany

#### 5.2 Rapid Application Specific Floating-point **Unit Generation with Bit-alignment**

Yee Jern Chong, Sridevan Parameswaran - Univ. of New South Wales, Sydney, Australia

#### 5.3s Dynamic Register File Resizing to Improve **Embedded Processor Performance and Energy**delay Efficiency

Houman Homayoun, Sudeep Pasricha, Mohammad Makhzan, Alexander V. Veidenbaum - Univ. of California, Irvine, CA

#### 5.4s C-based Design Flow: A Case Study on G.729A for Voice over Internet Protocol (VolP)

Mehrdad Reshadi, Bita Gorjiara,

Daniel D. Gajski - Univ. of California, Irvine, CA

#### PANEL: ELECTRONICS AND POLITICS: WHAT THE INDUSTRY NEEDS FROM THE INCOMING US **ADMINISTRATION**

#### Chair:

Pete Weitzner - Chapman Univ., Orange, CA

Tiffany Sparks - Chartered Semiconductor Manufacturing, Milpitas, CA

administration come into power. This could include a new party, and the US could elect the first woman or first African-American president. Closer to the DAC population, this election could be crucial for the Electronics Industry for any number of business or technology reasons. What, then, is going to be the most important platform to help boost the flagging technology sector? Where does the tech sector want the new administration to focus?

- Revising outsourcing policies

- Reducing visa restrictions

- Eliminating Sarbanes-Oxley and offering more tax incentives for startups

- Nationalized Health Care

- A reinvigorated technical program to recapture interest in science, similar to the space race in the 1960s

- Focus on math and science programs for middle and high schools

- Investing in more DARPA-like programs to promote research, innovation and new ideas to stimulate the economic growth engine

Panelists will debate which initiatives are most important for the DAC community and what changes candidates are talking about.

#### **Panelists:**

**Luc Burgun -** EVE, Palaiseau, France

**Todd Cutler -** Agilent Tech., Inc., Santa Clara, CA

Vicki Hadfield - SEMI North America,

Washinaton, DC

Russell Lefevre - IEEE, Washington, DC

Clayton Parker - Magma Design Automation, Inc.,

San Jose, CA

Chris Rowen - Tensilica, Inc., Santa Clara, CA

TOPIC AREA: BUSINESS

TOPIC AREA: ANALOG/MIXED-SIGNAL/RF AND SIMULATION

TOPIC AREA: SYSTEM-LEVEL AND EMBEDDED

SESSION 7

FOR DESIGNERS

RM: 206AB SESSION 8A

RM: 207ABC **SESSION 9**

rm: 208AB

#### SPECIAL SESSION: STUDENT DESIGN CONTEST

#### Chair:

Byunghoo Jung - Purdue Univ., West Lafayette, IN