# CONFERENCE PROGRAM & EXHIBITS GUIDE

JUNE 18-22, 2017 | AUSTIN, TX

SPONSORED BY:

# GET THE DAC APP!

## **DOWNLOAD FOR FREE!**

GET THE LATEST INFORMATION RIGHT WHEN YOU NEED IT.

DAC.COM

- Search the Technical Program

- Find Exhibitors

- Create Your

Personalized Schedule

Play DAC Attack & Win Prizes!

Visit **DAC.com** for more details and to download the **FREE** app!

## GENERAL CHAIR'S WELCOME

## Welcome to the Home of the 54<sup>th</sup> Design Automation Conference: Austin, Texas!

What does the future hold for EDA and IP? How did a small startup company reinvent power supplies? Will machines understand human emotion? What's the opportunity for innovation in China?

These are just a few of the thoughtprovoking presentations you'll find in this year's 54th Design Automation Conference program, which I'm honored to share with you. Here are some additional highlights from throughout the week and I hope to see you around the conference:

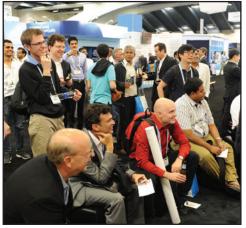

**Exhibits:** We assembled hundreds of the finest vendors of design automation tools and IP, with the best products available to the market, some announced to the world for the first time this week! Our exhibitors are eager to meet with you, learn about your design and verification challenges, and discover how they can help you overcome these challenges with better methodologies using the tools you own; or how you can apply new tools to get even better results, more quickly, and with more predictable design cycles. Visit our exhibitors on the main floor of the Convention Center Monday through Wednesday from 10:00 am until 6:00 pm.

Conference: We selected the best 160 original research papers on new technical work in our area, and assembled these into a technical program together with a dozen special sessions on the most current topics in both the core of design automation, as well as in related areas including Security, Internet of Things, Automotive, Machine Learning, Intellectual Property, and Embedded Software and Systems. As a conference within the conference, attendees of the DAC Research Program enjoy a special access lounge on the top floor of the Convention Center, the Research Grove. You gain access to this very special program with the DAC Full Conference Pass.

**Design:** We've verified a Designer Track of 8 invited sessions, 2 panels and the best 48 papers where users of design automation technology share their experiences in using cutting edge tools to solve the most difficult problems; enabling you the audience to learn from their experiences and achieve better success in your practical design and verification experiences.

**IP:** We've assembled an IP Track with 3 invited sessions, 4 panels and the best 12 submitted papers on how to choose, deploy, monetize and reduce your design complexity and risk by employing IP in your next design. You gain access to the Design and IP Tracks with the Designer Special Pass.

**Education:** We've created an education program with 9 tutorials on Monday and 6 training sessions on Thursday to enable you to gain insight into topics that while mainstream, might not be areas where you personally have the expertise that you would like to have. Access these educational opportunities by purchasing the

Monday Tutorial Pass and also sign up for the Thursday Training Sessions that attract your interest at the DAC website.

Keynotes: IoT is everywhere this year, and our 9:00 am Keynotes reflect this. Joe Costello opens the day on Monday, telling us about his IoT startup, "Enlighted," which is bringing automation to commercial and industrial buildings. Chuck Grindstaff begins our Tuesday sharing with us the many reasons why Siemens bought Mentor Graphics; I suspect one is to enable the joint company to be an even better design partner for your teams developing IoT products. Tyson Tuttle starts Wednesday off for us, sharing with us the unique challenges of providing Silicon IP for IoT, and how companies like his are meeting these challenges. Professor Rosalind Picard opens Thursday, sharing with us the surprising things she has learned in her research at the MIT Media Lab on teaching machines to understand human emotions.

SkyTalks: Just after lunch we present educational talks from those deeply involved in the business or technology of design. On Monday, listen to Professor Shojun Wei share with us the explosive growth of the Chinese IC industry, and some of the unique challenges and opportunities of this amazing expansion. On Tuesday, enjoy a friendly argument between long friends Simon Segars and Lucio Lanza as they debate how developing and deploying products for IoT will upset our market and change the world; and jot down their predictions of who will be the winners and losers in the market place. On Wednesday listen to Dinesh Ramanathan describe how his company has reinvented the power supply! Today's power conversion was developed in the 1980's and provides about 85% efficiency in converting AC to DC for our semiconductors - the rest is wasted as heat. His company's new technology, and new transistors convert power at greater than 95% efficiency - which is extremely interesting to anyone running huge data centers, electric motors for cars, or big solar arrays.

How are you going to navigate all of this? Well, you are holding the paper guide to find out what to do when! Read through this guide, mark each event, talk, panel, exhibit, session, and tutorial you want to see, and bring this with you every day, all week long. Or, if you are not that organized, **Download the DAC APP** from iTunes or Google Play, and mark the events and booths you want to see, and your phone will take you where you need to be, when you need to be there!

And, I expect to see each one of you at the networking events Sunday night, and each evening after the show, and at the evening venues up and down 6<sup>th</sup> Street!

Mac

Michael 'Mac' McNamara General Chair, 54<sup>th</sup> DAC

# TABLE OF CONTENTS

| General Chair's Welcome1                  | Wednesday Keynote51                           |

|-------------------------------------------|-----------------------------------------------|

| Conference Sponsors                       | Wednesday Sessions 52                         |

| Important Information 6                   | Wednesday Design/IP Track Poster Session . 65 |

| Networking Receptions7                    | Wednesday Work-in-Progess Poster Session67    |

| Keynotes 8                                | Thursday Keynote71                            |

| SKY Talks10                               | Thursday Sessions72                           |

| In Memory11                               | Thursday is Training Day 82                   |

| Workshops14                               | Colocated Conferences 87                      |

| Opening Session & Awards16                | Additional Meetings 89                        |

| Monday Keynote 17                         | DAC Pavilion - Booth 1737 97                  |

| Monday Sessions18                         | Executive Committee 103                       |

| Monday Design/IP Track Poster Session 23  | Exclusive Sponsorships 104                    |

| Monday Tutorials25                        | Platinum, Gold & Silver Sponsors 105          |

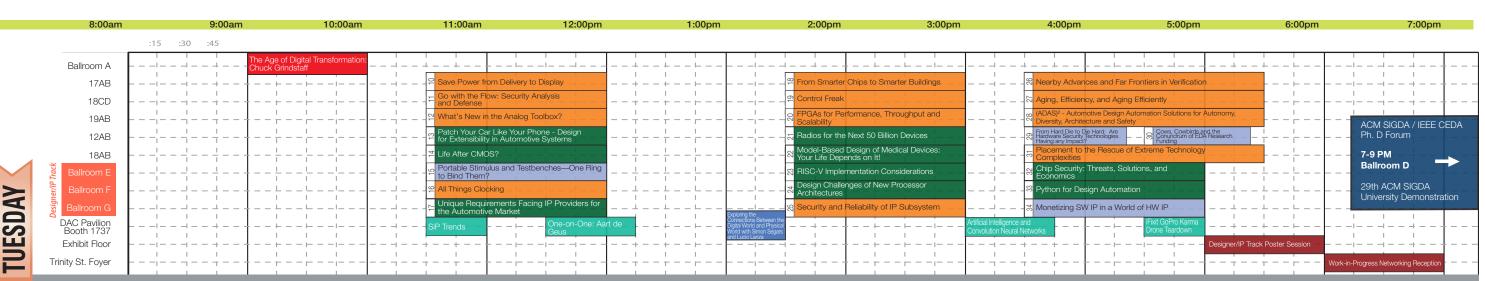

| Tuesday Keynote33                         | Exhibiting Companies 106                      |

| Tuesday Sessions34                        |                                               |

| Tuesday Design/IP Track Poster Session 46 |                                               |

| Tuesday Work-in-Progess Poster Session 48 |                                               |

## CONFERENCE SPONSORS

**ACM/SIGDA**

► IEEE/COUNCIL ON ELECTRONIC DESIGN AUTOMATION

ELECTRONIC SYSTEM DESIGN ALLIANCE

### DAC ATTACK GAMING RULES & ACHIEVEMENTS

Game Begins: 10:00am, Monday, June 19 | Game Ends: 4:00pm, Wednesday, June 21

#### **HOW DO I GET POINTS?**

1. Scan the QR Code at each participating exhibitor booth located on the DAC Exhibit Floor

There are different point categories for the exhibitors:

All Exhibitors 50 points 75 points Reception Sponsor

Amiq: Booth 1639

I Love DAC Sponsors 100 points

ClioSoft: Booth 613 OneSpin: Booth 1547 TrueChip: Booth 741

**Platinum Exhibitors** 125 points

Cadence: Booth 107 Synopsys: Booth 149

#### Encounter the World of IoT: Booth 521

- Maker's Market

- Find Your IP at DAC

- Teardowns

- VR Experience: Enter Another Realm of Reality

• Find your IP @ DAC

All activities part of DAC ATTACK Download the App and Play to Win

Participate in the activities listed below located throughout the show floor and scan the individual QR codes (each QR code can only be scanned once): Virtual Reality Experience in World of IoT Pavilion, Virtual Reality Experience in DAC Entertainment Lunch Corral, TechShop Puzzle Experience in World of IoT Pavilion, TechShop Puzzle Experience in DAC Entertainment Lunch Corral, and Roving DAC Magician.

4. Find the missing treasure hidden around the show each day: 150 points

This gets you the most points! Each day of the exhibit (Monday, Tuesday and Wednesday) DAC will hide Elliott, the Engineering Superhero action figure. Elliott will have a QR code on him, scan the code and earn the point. Please return Elliott to his hidden area for the next person to find.

5. Attend the morning key notes: 20 points

Scan the QR code at the end of each morning's keynote.

#### **PRIZES**

DAC Attack ends at 4:00pm on June 21st. Raffle prizes and the grand prize winner will be announced on Wednesday, June 21, 2017, at 5:00pm at the DAC Pavilion and by broadcast message within the App.

Registered attendees are eligible to win any of the prizes! There are two types of prizes: raffle prizes and the grand prize. Raffle winners will be selected from the top 50% of highest points scored. The Grand Prize will be randomly selected from the top 10% of the highest points scored.

#### **Grand Prize:**

Samsung Virtual Reality Headset

#### Raffle Prize:

Bose Wireless Headphones - \$150 Gift Card to the Amazon Store - Google Home - Nest Cam Outdoor Security System

#### **RULES AND HELPFUL INFORMATION**

- Please play fair! We reserve the right to remove points that were obtained in a fraudulent manner.

- Look for the QR markers around the exhibit fl oor located at each booth. If you do not see a QR code, ask the exhibitor where they are placed. Each code you scan through the DAC Mobile App earns you a variety of points that go towards your total tally.

- Check the leaderboard in the app or the Social Media boards at the show to see how many points you have, and where you stand on the leaderboard. Please note that the leaderboard updates approximately every 5 minutes.

- Registered attendees are eligible to win any of the prizes! Exhibitors and exhibit staff are not eligible to win.

- · As some prizes may be shipped to winning contestants, you do not need to be present to win.

### DAC ATTACK MOBILE APP GAME IS BACK!

Be Part of the Experience! Visit Exhibitors. Collect Points. Win Big.

DAC ATTACK Mobile App Game is Back - Be Part of the Experience! Visit Exhibitors. Participate in Activities. Collect Points. Win Big. Go big or go home the DAC Mobile App Game - DAC Attack is a mobile-enhanced persistent game that allows you to collect points throughout the DAC exhibit floor. Use your iOS or Android mobile devices to scan QR markers wherever you see them located in various exhibitors' booths and at activity centers.

Have fun and meet people as you make your way towards becoming one of this year's big winners!

Raffle prizes and the grand prize winner will be announced on Wednesday, June 21, 2017, at 5:00pm at the DAC Pavilion. As some prizes may be shipped to winning contestants, you do not need to be present to win.

**Grand Prize:** Samsung Gear Virtual Reality Headset

Raffle prizes: Bose Wireless Headphones

\$150 Gift Card to the Amazon Store

Google Home

**Bose Wireless Headphones**

**Nest Cam Outdoor Security System**

Visit **DAC.com** for more details and to download the **FREE** app!

## CONFERENCE INFORMATION

### **EXHIBIT HOURS**

#### **LOCATION: EXHIBIT HALLS 1-4**

Monday, June 19 10:00am - 6:00pm Tuesday, June 20 10:00am - 6:00pm Wednesday, June 21 10:00am - 6:00pm

#### **REGISTRATION HOURS** ▶ ▶ ▶

### LOCATION: AUSTIN CONVENTION CENTER ATRIUM

Friday, June 16 - Sunday, June 18 8:00am - 6:00pm Monday, June 19 - Wednesday, June 21 7:00am - 7:00pm Thursday, June 22 7:00am - 5:00pm

Thank You to Our Sponsor

#### **ONLINE PROCEEDINGS**

DAC Proceedings and tutorials will be delivered electronically online via a username and password.

To access: http://proceedings.dac.com Username = Email address

Password = Registration ID (on your badge)

Please refer to your registration receipt to be reminded of what package and associated files you are eligible to view.

#### STAY CONNECTED

#### **WIRELESS INTERNET**

Austin Convention Center has complimentary wireless internet service throughout the facility.

## "BIRDS-OF-A-FEATHER" ▶ ▶ ▶ ▶ MEETINGS

DAC will provide conference rooms for informal groups to discuss items of common technical interest. These very informal, non-commercial meetings, held after hours, are referred to as "Birds-of-a-Feather" (BOF). All BOF meetings are held at the Austin Convention Center, Tuesday, June 20 from 7:00 - 8:30pm.

To arrange a BOF meeting, please contact Corinne@dac.com. An LCD projector and screen will be provided.

#### FIRST AID ROOM

First Aid Room is located between Exhibit Halls 3 & 4 on the Trinity Street side of the building.

First Aid Room Hours:

Saturday, June 17 - Sunday, June 18: 8:00am to 6:00pm Monday, June 19 - Thursday, June 22: 7:00am to 7:00pm

Non-emergency: 311

In-house security: 512-404-4111

### DAC MOBLE APP

Download the DAC App!

Review the conference program, find exhibitors, and create a personalized schedule all from your phone or mobile device.

The DAC App is **FREE** for registered attendees! Check your email for your personalized invite or visit DAC.com for more information

## DAC NETWORKING OPPORTUNITIES

### WELCOME RECEPTION

Sunday, June 18 5:30 - 7:00pm | 4th Floor Foyer

Join fellow attendees for the first event to network and kick-off DAC 2017!

#### **DESIGNER/IP TRACK POSTER** NETWORKING RECEPTION

Monday, June 19 - Wednesday, June 21 5:00 - 6:00pm each day | Exhibit Hall 1

Join us in Exhibit Hall 1 and while viewing the Designer and IP Track posters, take part in networking with light hors' d' oeuvres and beverages.

Thank You to Our Sponsors

Tuesday, June 20 6:00 - 7:00pm | Trinity St. Foyer

Join us in the Foyer to see Work-in-Progress posters and enjoy light hors' d'oeuvres and beverages.

**NETWORKING RECEPTION** ▶ ▶

Thank You to Our Sponsor

#### **NETWORKING RECEPTION** ▶ ▶

Wednesday, June 21 6:00 - 7:00pm | Trinity St. Foyer

Join us in the Foyer to see Work-in-Progress posters and enjoy light hors' d'oeuvres and beverages.

### **NETWORKING RECEPTION**

Monday, June 19 6:00 - 7:00pm | Trinity St. Foyer

Join attendees for refreshments and lively discussion recapping the day's events.

Thank You to Our Sponsor

#### **NETWORKING RECEPTION** ▶ ▶

Thursday, June 22 5:30 - 6:30pm | 4th Floor Foyer

Join attendees for refreshments and lively discussion recapping the day's events.

## KEYNOTE PRESENTATIONS

## **KEYNOTE:** IOT: TALES FROM THE FRONT LINE

JOE COSTELLO - Enlighted, Inc., Sunnyvale, CA

Monday, June 19 | 9:15 - 10:00am | Ballroom A

There is a lot of talk about the potential of the Internet of Things. But what is happening on the front lines? Where are the examples of real impact?

Enlighted CEO Joe Costello will discuss how the IoT is impacting commercial real estate, the largest asset class in the world, by giving buildings a "sensory system" akin to a human body. Once deployed, there are a multitude of new opportunities to improve business processes thanks to granular data that has never been available before.

Learn how this technology is currently being developed and applied, the challenges, along with predictions for the future of IoT in commercial buildings.

See page 17 for more details.

## **KEYNOTE:** THE AGE OF DIGITAL TRANSFORMATION

**CHUCK GRINDSTAFF** – Siemens PLM Software Inc., Plano, TX

Tuesday, June 20 || 9:00 - 10:00am || Ballroom A

EDA has continually moved to higher levels of abstractions, changing how electronics are designed and created. Now we are seeing the need in the industrial world for further digitalization and virtualization. In his keynote, Chuck Grindstaff, Executive Chairman of Siemens PLM Software, will discuss the global impact of this digital transformation. EDA pioneered this revolution and paved the way for today's digital industrial revolution that is transforming and disrupting all industries. For system companies, their products are evolving into advanced system of systems. As a result, SoCs and application software are now the core differentiation and enabling technologies. This is spurring growth and opportunity for IC designers in the convergence of semiconductor and systems. Siemens and Mentor together are setting the vision for this new era of digital transformation.

See page 33 for more details.

#### **KEYNOTE: ACCELERATING THE IOT**

**TYSON TUTTLE** – Silicon Labs, Austin, TX

Wednesday, June 21 || 9:00 - 10:00am || Ballroom A

The Internet of Things (IoT) has been hailed as the next frontier of innovation in which the everyday "things" in our homes, offices, cars, factories and cities connect to the Internet in ways that improve our lives and transform industries. The IoT market is poised to reach 70 billion connected devices by 2025, but several challenges remain in achieving the market's full potential. Tyson Tuttle, CEO of Silicon Labs, will explore what it will take to accelerate the promise of the IoT. In his keynote, Tyson will consider the market imperatives and engineering challenges of adding connectivity to electronic devices, including cost, ease of use, energy efficiency, interoperability, future extensibility, and security. Addressing these challenges will unleash the limitless possibilities of a more connected world.

See page 51 for more details.

## **KEYNOTE:** EMOTION TECHNOLOGY, WEARABLES, AND SURPRISES

**ROSALIND PICARD** – Massachusetts Institute of Technology, Cambridge, MA

Thursday, June 22 || 9:10 - 10:00am || Ballroom A

Years ago, I set out to create technology with emotional intelligence, demonstrating the ability to sense, recognize, and respond intelligently to human emotion. At MIT, we designed studies and developed signal processing and machine learning techniques to see what affective insights could be reliably obtained. In this talk I will highlight the most surprising findings during this adventure. These include new insights about the "true smile of happiness," discovering new ways cameras (and your smartphone, even in your handbag) can compute your bio-signals without using any new sensors, finding electrical signals on the wrist that reveal insight into deep brain activity, and learning surprising implications of wearable sensing for autism, anxiety, sleep, memory, epilepsy, and more. What is the grand challenge we aim to solve next?

See page 71 for more details.

## SKY TALKS

### SKY TALK: CHINA'S IC INDUSTRY: TODAY AND TOMORROW – ITS INFLUENCE ON GLOBAL DESIGN AND DESIGN AUTOMATION COMMUNITY

Shaojun Wei - Professor, Tsinghua Univ., Beijing, China

Monday, June 19 | 1:00 - 1:25pm | DAC Pavilion - Booth 1737

See page 19 for more details.

# SKY TALK: EXPLORING THE CONNECTIONS BETWEEN THE DIGITAL WORLD AND THE PHYSICAL WORLD WITH SIMONS SEGARS AND LUCIO LANZA

► Tuesday, June 20 | 1:00 - 1:25pm | DAC Pavilion - Booth 1737

Simon Segars - Chief

Executive Officer, ARM

Ltd., Cambridge,

United Kingdom

See page 38 for more details.

Lucio Lanza – Managing Director, Lanza TechVentures, Palo Alto, CA

See page 56 for more details.

## **SKY TALK:** POWER ELECTRONICS WITH VERTICAL Gan DEVICES

**Dinesh Ramanathan** – Chief Executive Officer, NexGen Power Systems, Inc., Cupertino, CA

► Wednesday, June 21 | 1:00 - 1:25pm | DAC Pavilion - Booth 1737

## IN MEMORY

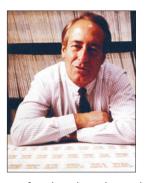

## Robert M. Gardner | 1943 - 2017

Mr. Gardner was member of the Board of Directors for Verific Design Automation since its inception in 1999. He co-founded Missing Link Electronics in 2008 and was its president and chief operating officer at the time of his death.

Mr. Gardner served as the executive director of the Electronic Design Automation (EDA) Consortium, now the Electronic System Design (ESD) Alliance, from 2007 until 2015. In 2016, he was presented with the DATE Fellow Award by the Design Automation and Test in Europe (DATE) Conference and Exhibit in recognition of his long association with EDAC and DATE.

Over a 50-year career, Mr. Gardner held senior management positions at semiconductor and EDA companies Signetics/Philips, AMD, Exemplar Logic, Design Acceleration, Bridges2Silicon, and ITeX. A 1965 graduate of California Polytechnic College in Pomona, he earned a Bachelor of Science degree in Electrical and Electronics Engineering. Mr. Gardner was active in instrumental music education and performances in Silicon Valley. He also was an avid sailor/yacht racer.

He is survived by his wife Monique; son Scott and his wife Sarah and children Zoe and Reese; daughter Lauree Walker and her husband Tim and their children Luke and Lily.

## Carl Harris | 1941 - 2017

Mr. Harris spent over 40 years in educational publishing where he worked for Prentice Hall, W.A. Benjamin, Allyn & Bacon, Butterworth, Addison Wesley, Kluwer Academic Publishers.

and Springer in a variety of positions from trade salesman to editorial director. Carl was particularly proud of his contribution to the field of Electrical Engineering through innovative publishing of advances in research and technology while at Kluwer Academic Publishers.

## IN MEMORY

## Ralph Otten | 1949 - 2016

Last September Ralph Otten passed away as a result of a tragic accident while on vacation in the Caucasian republic of Georgia. Ralph lived life to the fullest until literally the last moment: always curious, always informed and always with a quirky (but well-founded) opinion. With Ralph Otten the EDA community is losing a long

time contributor, educator and friend.

Ralph Otten received his PhD from Eindhoven University in the Netherlands in 1976. At IBM TJ Watson Research Center he was on the team that designed the pioneering

Yorktown Silicon Compiler, heralding the a new golden age for EDA. At DAC in 1982 Ralph published a key work on floor plan design that has influenced an entire generation of EDA researchers and set countless PhD students on a career in EDA. Later Ralph was full professor and educational director at Delft University of Technology, as well as Eindhoven University. In 2015 he retired and focused on his passions for Verdi, Italy and classical music.

Many of us will remember Ralph as a fixture at DAC, speaking, attending and reviewing for decades. He will be missed. Fortunately, Ralph's wife Carla will continue to assist DAC as before.

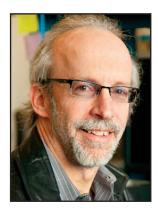

## Mark Templeton | 1959 - 2016

Mark Templeton, the CEO and co-founder of Artisan Components, was a man who revolutionized the proliferation and distribution of semiconductor IP and he was able to achieve this while keeping an attitude of politeness and intellectual generosity.

Though he originated the idea

for a company focused solely on component-level semiconductor IP and was the only CEO for the entire 14 year history of Artisan, Mark always introduced himself as the co-founder. He was modest about his success and profoundly grateful for the work of others: co-founders, employees, investors and partners, that he believed made the success possible.

After ARM acquired Artisan in 2004, Mark joined the board of ARM and was very proud to see Artisan become a significant and strategically crucial part of what was clearly going to be the leader of the expanding IP world.

"He was a great leader because he was always able to look far ahead at the distant horizon, while not taking his eyes off the path in front of him. He knew when it was time to stop and execute and took great care to get all the little things right," said Lucio Lanza, the first investor in Artisan Components.

Mark had an insatiable curiosity and never stopped learning. He loved to share new insights with his team at Artisan and his friends in the industry through the exciting years of Artisan. After Artisan and ARM, Mark continued to satisfy his intellectual curiosity by taking classes at Stanford and San Jose State, and teaching himself modern coding techniques.

Mark was always willing to help young entrepreneurs, new companies, and take meetings with people with only an idea. He never ceased learning from these meetings and never stopped sharing and teaching his insights to others. He was learning and teaching up until his very last days.

Mark was very successful because he was well balanced. He was usually right but never arrogant. Most importantly, he always found the appropriate balance between the demands of a start-up, and later a large growing company, and his family. Mark cherished the time he spent with his wife Betsy, and his two children, by whom he is now survived.

## IN MEMORY

## Charles "Chuck" Shaw | 1925 - 2017

Chuck Shaw, former SIGDA chairman, recently passed away. He died peacefully in his home on February 24, 2017, surrounded by three of his kids and a daughter-in-law.

Chuck was instrumental in moving SIGDA from a small group of engineers with an interest in EDA to a thriving

professional society with numerous programs in place to advance the profession. To be sure, there were many contributors involved in implementing these programs but it was Chuck's leadership and enthusiasm that transformed the organization.

When Chuck was elected chairman of SIGDA in 1983 the SIGDA newsletter was our only publication and we provided seed money for 2 workshops. By the time his term ended in 1991, SIGDA was a sponsor, co-sponsor or working-in-conjunction-with 20 professional meetings. We also had programs in place to put EDA literature on CD-ROM, a University Booth at DAC, a benchmark program to compare DA algorithm performance, travel and library grants, video tape production of DA lectures and a new journal in the planning process.

Chuck achieved this remarkable transition by restructuring the board of directors. Quoting from his farewell "Letter from the Chair" in the June 1991 issue of the newsletter:

I set as a prerequisite for Board membership that each person be the implementer of a major project. A person becomes a Board member by proposing or accepting a major project and selling it to the existing Board. He/she then joins the Board to carry it out. The other members of the Board serve as the reviewers, to whom each Board member reports the progress of his/her project(s). The whole Board sets policy. This has worked magnificently.

Magnificently, indeed! It attracted many hard working professionals with bright ideas onto our board and it remains the structure of the SIGDA Board of Directors to this day.

Chuck's enthusiasm and work ethic were contagious. He served 8 years as SIGDA Chairman and 11 years on DAC Executive committee (85-95) all while pursuing a very successful career at GE/Intersil and Cadence Design Systems. He will be sorely missed and long remembered by all of us in EDA.

Michael Lorenzetti

Former SIGDA Chairman

## WORKSHOPS

W1

## WORKSHOP 1: SECOND INTERNATIONAL WORKSHOP ON DESIGN AUTOMATION FOR CYBER-PHYSICAL SYSTEMS (DACPS)

Time: 8:30am - 4:30pm | | Room: 17AB | | Event Type: Workshop Track: EDA, Design | | Topic Area: General Interest, Codesign & System Design

#### **ORGANIZERS:**

Xin Li - Carnegie Mellon Univ., Pittsburgh, PA

Mohammad Al Faruque - Univ. of California, Irvine, CA

Shiyan Hu - Michigan Technological Univ., Houghton, MI

Yier Jin - Univ. of Central Florida, Orlando, FL

Rajiv Ranjan - Newcastle Univ., Callaghan, Australia

Bei Yu - Chinese Univ. of Hong Kong, Shatin, Hong Kong

Huafeng Yu - Boeing, Huntsville, AL

Qi Zhu - Univ. of California, Riverside, CA

Cyber-Physical Systems (CPS) are characterized by the strong interactions among cyber components and dynamic physical components. CPS system examples include automotive and transportation systems, smart home, buildig and community, smart battery and energy systems, surveillance systems, cyber-physical biochip, and wearable devices.

Due to the deeply complex intertwining among different components, CPS designs pose fundamental challenges in multiple aspects such as performance, energy, security, reliability, fault tolerance and flexibility. Innovative design automation techniques, algorithms and tools that addressing the unique CPS challenges, such as the fast increase of

system scale and complexity, the close interactions with dynamic physical environment and human activities, the significant uncertainties in sensor readings, the employment of distributed architectural platforms, and the tight real-time constraints, are highly desirable.

This workshop will present the state-of-the-art research results on the topic of design automation for CPS, and stimulate the CAD researchers to participate in the interdisciplinary CPS research area in the future.

#### **SPEAKERS:**

Jiang Hu - Texas A&M Univ., College Station, TX

Tei-Wei Kuo - National Taiwan Univ., Taipei, Taiwan

Ramesh S - General Motors Research and Development, Warren, MI

Ulf Schlichtmann - Technische Univ. München, Germany

Rahul Mangharam - Univ. of Pennsylvania, Philadelphia, PA

Mohammad Al Faruque - Univ. of California, Irvine, CA

Yier Jin - Univ. of Central Florida, Orlando, FL

W2

## WORKSHOP 2: DAC WORKSHOP ON AUTONOMOUS VEHICLES, AVIONICS, TRANSPORTATION, AND ROBOTICS (AVATAR)

Time: 9:00am - 5:00pm || 12AB || Track: Automotive, Design Topic Area: General Interest, Codesign & System Design, Emerging Architectures & Technologes || Event Type: Workshop

#### **ORGANIZERS:**

Rasit Topaloglu - IBM Corp., Hopewell Junction, NY Peng Li - Texas A&M Univ., College Station, TX Huafeng Yu - Boeing, Huntsville, AL

There have been significant development efforts in autonomous systems in the last decade. We have already started to see successful realization of products that utilize autonomous design and algorithms. Particular achievements have come in vehicle, avionic, and robotic applications. There are still research and development challenges in these systems though and some of these challenges do intersect with the interest of the design automation community. Thus, we would like to hold a workshop to facilitate interaction between autonomous system and design automation communities.

The EDA community has a long history developing a full spectrum of modeling, optimization, design verification and test algorithms and tools for electronic systems. We expect that the strong expertise accumulated in EDA over the past few decades may be well extended for the targeted application areas of this workshop, which, if successful, will stimulate new

advancements in autonomous systems and broaden the impacts of EDA research in general.

To realize these goals, we plan to have a full-day workshop with invited talks and panel sessions. We target holding three sessions and invite the following list of speakers. We anticipate being able to understand the challenges they face and discuss if some of the problems can be solved using the skills and experience of the design automation community.

#### **SPEAKERS:**

Rahul Mangharam - Univ. of Pennsylvania, Philadelphia, PA

Kara Kockelman - Univ. of Texas at Austin, TX

Nicholas Gans - Univ. of Texas at Dallas, Richardson, TX

Ignacio Alvarez - Intel Corp., Portland, OR

$\textbf{Ivan Lozano} \ \textit{-} \ \textit{Airspace Systems Inc., San Francisco, CA}$

Gaurav Bansal - Toyota InfoTechnology Center, Mountain View, CA Alireza Talebpour - Texas A&M Univ., College Station, TX W3

#### **WORKSHOP 3: CUSTOMIZING PDKS FOR DESIGN-SPECIFIC REQUIREMENTS**

Time: 9:00am - 12:00pm || 19AB || Track: Design, EDA

Topic Area: Analog & Mixed-Signal Design, Physical Design & DFM

**Event Type: Workshop**

#### **ORGANIZER:**

Ted Paone - Silicon Integration Initiative, Inc., Austin, TX

Good stories often start over a beer. While sharing a libation or n+1 with several friends from the industry, one of them mentioned a problem with their fab supplied PDK. Another had a similar problem with a different PDK, by the end next round, I had collected a list of common problems that design groups were having with their PDKs.

A process design kit (PDK) models a specific fabrication process for a set of tools used in the design flow blessed by the fab. Using this PDK and following one of the fab supported design flows, the designers can create and verify a design that is manufacturable in that process.

The PDKs available from the fabs not only reflect the specific manufacturing process but can be tailored for markets with the addition of processing steps and devices. This generic PDK works very well for many of the design groups. You can create a design and it can be manufactured.

With the competition in some markets, the design groups must take any advantage it can over its competitors. They choose the tools and methodologies specific to their design market and design style, these may deviate from the supported flows. These groups want to enhance the PDK to meet their needs. It isn't just a drinking problem; these issues are industry wide. An industry wide problem can be solved with a collaboratively developed solution.

In this tutorial, we will explore ways of customizing PDKs to support the tools and devices in your design flow without rewriting the existing PDKs. We will jump in with parameters, resetting defaults and other control and adding new parameters. On to PCells, customize the shapes, connectivity and properties without source code. Add new tools to the flow, integrating the technology and supporting new parameters and models. Integrate your own devices into the PDK and not have them overwritten on an uprev from the fab.

These solutions addressed many of the problems seen by the PDK Users. They represent what can be done by working collaboratively to solve common problems yet allowing each user to customize the implementation.

Working together to address common issues, under the anti-trust protections provided by Si2 membership, SIG members create ideas, write white papers, conduct surveys, and develop prototypes; unique solutions sharing a common understanding of the problems.

#### **SPEAKER:**

Ted Paone - Silicon Integration Initiative, Inc., Austin, TX

W4

#### **WORKSHOP 4: LEADERSHIP IMPROV**

The purpose of this workshop is to enhance your capacity to lead technology organizations effectively.

Why are some leaders better and more successful than others? One reason involves their ability to communicate with others in the moment, to be mindful and respond to what is happening right now. We borrow techniques from improv to help you learn to better communicate with others.

Improv requires skill, preparation and practice to be able to listen, act and react in the moment. This improv workshop prepares both individual contributors and leaders how to react, adapt and communicate honestly with others.

We use real world examples and cases to make this workshop immediately applicable to your workplace.

You will learn how to listen, ask questions to learn more about your boss or subordinate's goals, objectives and interests, and to respond in ways that improve understanding and cooperation.

The word "improv" brings to mind improv comedy and laughter. While this class is serious business, the workshop is engaging and entertaining while you learn.

In this highly participative class, we use case studies and real-world scenarios from the tech industry, which provide you the opportunity to learn new techniques and put them to immediate use.

#### SPEAKER:

Leslie Martinich - IEEE, Austin, TX

## MONDAY, JUNE 19

See More Great Content in the DAC Pavilion! Complete schedule can be found on Pages 97 - 101, Additional Meetings: See Pages 89 - 95.

#### **OPENING SESSION & AWARDS PRESENTATION**

Time: 8:45 - 9:15am | | Room: Ballroom A | | Topic Area: General Interest

Join us as we set the stage for the 54th DAC! DAC's Executive Committee will highlight the conference's events, and the award presentations will recognize success and excellence for individuals in the industry.

### 2016 PHIL KAUFMAN AWARD FOR DISTINGUISHED CONTRIBUTIONS TO EDA

Dr. Andrzej Strojwas, Keithley Professor of Electrical & Computer Engineering, Carnegie Mellon University, Pittsburgh, PA

Dr. Strojwas is being recognized for his pioneering and sustained contributions to design for manufacturing.

#### **IEEE CEDA OUTSTANDING SERVICE AWARD**

Charles Alpert, Cadence Design Systems, Inc.

For outstanding service to the EDA community as DAC General Chair in 2016.

#### **IEEE FELLOW**

#### Luca Carloni, Columbia University

For contributions to system-on-chip design automation and latency-insensitive design.

#### **IEEE FELLOW**

#### Xin Li, Duke University / Duke Kunshan University

For contributions to modeling, analysis, and optimization of variability of integrated circuits and systems.

#### **IEEE FELLOW**

#### Frank Liu, IBM Research

For contributions to design for manufacturability of VLSI circuits.

#### **IEEE FELLOW**

#### Walden C. Rhines, Mentor, A Siemens Business

For leadership and technology innovation in integrated circuit design and automation.

#### **IEEE FELLOW**

#### Weiping Shi, Texas A&M University

For contributions to modeling and design of VLSI interconnects.

#### **IEEE CEDA DISTINGUISHED SERVICE AWARD**

William H. Joyner, Jr., Semiconductor Research Corporation, Retired

For going above and beyond the call of duty in support of CEDA's activities.

## IEEE TRANSACTIONS ON COMPUTER-AIDED DESIGN OF INTEGRATED CIRCUITS AND SYSTEMS DONALD O. PEDERSON BEST PAPER AWARD

Xiaoqing Jin, Alexandre Donzé, Jyotirmoy V. Deshmukh, and Sanjit A. Seshia

"Mining Requirements from Closed-Loop Control Models," Vol. 34, Issue 11, pp. 1704 - 1717, November 2015.

### A. RICHARD NEWTON TECHNICAL IMPACT AWARD IN ELECTRONIC DESIGN AUTOMATION

Matthew W. Moskewicz, Univ. California, Berkeley/ Cadence; Conor F. Madigan, Kateeva, Inc.; Ying Zhao, Wuxi Venture Capital Group; Lintao Zhang, Microsoft Research Asia; Sharad Malik, Princeton Univ.

Sponsored by the IEEE Council on EDA and the ACM Special Interest Group on Design Automation. For seminal contributions to scalable Boolean satisfiability solving including locality-based search and efficient backtracking.

Matthew W. Moskewicz, Conor F. Madigan, Ying Zhao, Lintao Zhang, and Sharad Malik "Chaff: Engineering an Efficient SAT Solver,"

Proc. of the 38th annual Design Automation Conference, pp. 530 - 535, June 2001.

#### 2017 ACM TODAES BEST PAPER AWARD

Farshad Firouzi, Fangming Ye, Krishnendu Chakrabarty, Mehdi B. Tahoori

"Aging- and Variation-Aware Delay Monitoring Using Representative Critical Path Selection" ACM Design Automation of Electronic Systems, Vol. 21, Issue 1, Nov. 2015.

### **ACM SIGDA OUTSTANDING NEW FACULTY AWARD Yier Jin. University of Central Florida**

### ACM SIGDA OUTSTANDING PH.D. DISSERTATION AWARD

Jeyavijayan Rajendran – "Trustworthy Integrated Circuit Design," New York University

Advisor: Ramesh Karri

#### **ACM FELLOW**

#### Sachin Sapatnekar

For contributions to the enhancement of performance and reliability in integrated circuits.

#### **ACM FELLOW**

#### Raiesh Gupta

For contributions in design of embedded systems and hardware-software codesign.

### 2017 MARIE R. PISTILLI WOMEN IN ENGINEERING ACHIEVEMENT AWARD

Janet Olson, Vice President of Engineering for RTL Synthesis R&D at Synopsys, Inc

This annual award, named for Marie R. Pistilli, the former organizer of DAC, recognizes individuals who have visibly helped advance women in Electronic Design.

#### P.O. PISTILLI UNDERGRADUATE SCHOLARSHIP FOR ADVANCEMENT IN COMPUTER SCIENCE AND ELECTRICAL ENGINEERING

#### Kenia Hale, Yale University

The objective of the P.O. Pistilli Undergraduate Scholarship for Advancement in Computer Science and Electrical Engineering is to increase the pool of professionals in Electrical and Computer Engineering and Computer Science from under-represented groups (female, African-American, Hispanic, Native American, and disabled students). In 1989, ACM Special Interest Group on Design Automation (SIGDA) began providing the program. DAC funds a \$4000 scholarship, renewable up to five years, to graduating high school seniors who have a 3.00 GPA or better (on a 4.00 scale).

#### **UNDER-40 INNOVATORS AWARD**

The Under-40 Innovators Award is new this year and is sponsored by Association for Computing Machinery (ACM), the Electronic Systems Design Alliance (ESDA), and the Institute of Electrical and Electronics Engineers (IEEE). The award will recognize the top five young innovators (nominees should be 40 years or younger in age as of June 1, 2017) who are movers and shakers in the field of design and automation of electronics

## MONDAY, JUNE 19

## **KEYNOTE:** IOT: TALES FROM THE FRONT LINE

JOE COSTELLO - Enlighted, Inc., Sunnyvale, CA

► Time: 9:15 - 10:00am | | Room: Ballroom A

Track: IoT | | Emerging Architectures & Technologies,

Embedded System Software, General Interest

There is a lot of talk about the potential of the Internet of Things. But what is happening on the front lines? Where are the examples of real impact?

Enlighted CEO Joe Costello will discuss how the IoT is impacting commercial real estate, the largest asset class in the world, by giving buildings a "sensory system" akin to a human body. Once deployed, there are a multitude of new opportunities to improve business processes thanks to granular data that has never been available before.

Learn how this technology is currently being developed and applied, the challenges, along with predictions for the future of IoT in commercial buildings. **Biography:** Joe Costello has been a high tech executive and CEO for the last 28 years. He became the CEO of Cadence Design Systems in 1987 and worked with the company from its inception until it became the largest electronic design automation (EDA) company in the world, with over a billion dollars in annual revenue.

Since the early 90s, Joe has been the mastermind behind numerous start-ups based around the idea of the Internet of Things, even before the phrase was even coined. Specifically, Joe started an incubator in 2000 and worked on IoT from late 2000 – 2004. That incubator included Orb Networks, which pursued IoT for entertainment-oriented applications and led to the creation of a platform for media distribution, management and control called AllPlay. Qualcomm acquired Orb Networks in 2013 and Joe joined its Qualcomm IoT platform group to help spearhead the creation and promotion of AllJoyn.

Costello was named the top CEO of America in 1997 by Chief Executive Magazine. In recognition of his service to the EDA industry, he was awarded the Phil Kaufman award in 2004, the highest accolade in the EDA industry. Costello has also served as a board member of dozens of companies including Oracle, Macromedia, Clarify and Mercury Interactive as well as numerous private companies.

#### **ABOUT ENLIGHTED**

Designed to change everything, Enlighted provides the world's most advanced digital sensor and analytics platform for smarter buildings to Fortune 500 companies around the globe. The company is headquartered in Sunnyvale, CA.

1

#### **DESIGNER TRACK: VERIFICATION AUSTIN STYLE!**

Time: 10:30am - 12:00pm | Room: Ballroom E | Event Type: Invited Presentations Track: Design, IP | | Topic Area: Test & Verification, Simulation & Timing Analysis, General Interest

#### **CHAIR:**

Hemendra Talesara - Synapse Design, Austin, TX

#### **ORGANIZER:**

Harry Foster - Mentor, A Siemens Business, Plano, TX Hemendra Talesara - Synapse Design, Austin, TX

Austin has quickly become one of the leading centers of verification expertise within the US and the world. This session invites three internationally recognizable names in verification (all from Austin) and showcases what makes Austin so unique. Each invited speaker will not only describe the challenges and unique solutions they have implemented—but their general philosophy in building a world class verification team.

#### 1.1 Live Oak: Deep Roots of Verification & Design for Verification in Austin (10:30)

Wolfgang Roesner - IBM Systems and Technology Group, Austin, TX

1.2 Is it Hardware or Software? It's Both! (11:00)

Bill Greene - ARM, Inc., Austin, TX

1.3 Verification Challenges Associated with Automotive Microprocessors and Controllers (11:30)

Xiao (Sean) Sun - NXP Semiconductors, Austin, TX

Thank You to Our Sponsor

2

#### **DESIGNER TRACK: PHYSICAL DESIGN - NUGGETS FROM THE TRENCHES**

Time: 10:30am - 12:00pm | | Room: Ballroom F | | Event Type: Reviewed Presentations | | Track: Design, EDA | | Topic Area: Physical Design & DFM, **Digital Design**

#### **CHAIR:**

Gary Ellis - Encore Semi Inc., Norman, OK

This session will highlight advanced techniques intended to expedite various areas of the physical design process. From the construction of very large designs using approaches like re-use and divide and conquer, to innovative tools for quicker ECOs and DRC sign-off, this session will help you to improve your design process.

#### 2.1 Enabling Reuse of Logic Blocks Integrated Specialty Intellectual Property (IP) Blocks (10:30)

Sudeep Mandal, Mukesh Bagul - GLOBALFOUNDRIES, Bengaluru, India Rashmi Chatty - GLOBALFOUNDRIES, Austin, TX Liang Ge - GLOBALFOUNDRIES, Shanghai, China Karl Vinson - GLOBALFOUNDRIES, Essex Junction, VT

#### 2.2 Divide and Conquer Methodology for Ultra-Fast Layout Convergence (10:45)

Satya Seshadri, Sarath Kumar B, Sharath G, Murali Sundaram - Intel Technology India Pvt. Ltd, Bangalore, India

#### 2.3 Power Efficient Distribution of Pervasive Multi-Cycle Signals (11:00)

William R. Migatz - IBM Corp., Poughkeepsie, NY Shyam Ramji - IBM Corp., Yorktown Heights, NY

#### 2.4 Optimized Automation of Design Rule Violations (DRC) Fix (11:15)

Sudeep Mandal, Mirunalini Gunasekaran - GLOBALFOUNDRIES, Bengaluru, India

#### 2.5 Innovative Metal-Only ECO Methodology to Implement Large/ **Complex Functional ECOs (11:30)**

Biswajit Maity, Rajasekhara Badana, Arun Kandula, Abhishek Banthia, Viren R. Gajjar, Roshan Bondse - Intel Technology India Pvt. Ltd, Bangalore, India

#### 2.6 Colorless Metal Routing for Triple and Quadruple Patterning **Technologies (11:45)**

Hyosig Won, Myungsoo Jang - Samsung Electronics Co., Ltd., Hwaseong-si, Republic of Korea

Hyounsoo Park - Samsung Electronics Co., Ltd., Yongin, Republic of Korea Dayeon Cho, Taehoon Kim - Samsung Electronics Co., Ltd., Hwaseong-si, Republic of Korea

Q &A Poster Session

Monday, June 19 5:00 - 6:00 - Exhibit Floor

Thank You to Our Sponsor

#### IP TRACK: SECURITY IP FOR IOT FROM SENSORS TO CLOUD

Time: 10:30am - 12:00pm | | Room: Ballroom G | | Event Type: Invited Presentations Track: IP, Security | | Topic Area: General Interest

#### **CHAIR:**

Claude Moughanni - Lattice Semiconductor Corp., San Jose, CA

The world of IOT promises the conveniences of remotely accessing our personal information and controlling the devices that permeate our private and working lives 24 hours a day. Being always connected means we are always vulnerable to security breaches. This session deals with evolving approaches in HW and SW security IP from sensors to the cloud, touching on securing access to devices, interfaces between them and corresponding data content.

#### 3.1 Authenticate Everything (10:30)

Pim Tuyls - Intrinsic ID, Sunnyvale, CA

**3.2 Challenges of the Emerging IoT Security Arena (11:00) Jacques Fournier**, Alain Merle - CEA-LETI, Grenoble, France

3.3 Security Assurance Guidance for Third Party IP (11:30)

Brent Sherman - Intel Corp., Hillsboro, OR

Thank You to Our Sponsor

# SKY TALK: CHINA'S IC INDUSTRY: TODAY AND TOMORROW - ITS INFLUENCE ON GLOBAL DESIGN AND DESIGN AUTOMATION COMMUNITY

Time: 1:00 - 1:25pm | | Room: DAC Pavilion - Booth 1737 | | Event Type: SKY Talk Track: Design, EDA | | Topic Area: General Interest

#### **ORGANIZER:**

Sharon Hu - Univ. of Notre Dame. IN

When China announced its national plan to promote its native IC industry, this raised many questions. With its rapid growth, China's IC industry is becoming an emerging force globally, increasing the importance of understanding the answers to these questions. Few people really understand China's IC industry. For example, what is the real state of the China's IC industry today, what implications does such a promotion have to the global IC, EDA and other related

industries, and what goals are China's IC industry working to achieve?

This presentation will give an overview of the Chinese IC market, followed by an introduction of China's IC industry with an emphasis on fabless companies. China's native products, design technologies, and talents will be described in detail to provide an objective and comprehensive picture of China's IC industry. In addition, China's current status in design automation technology and indigenous EDA companies will be discussed.

As China is a unique country with huge population, vast territory, rapidly growing but unbalanced economy, and many diverse cultures, life-styles and traditions, its native product demands are also diverse. How to meet these drastically different requirements with a reasonable time to market while keeping costs low presents a big challenge. A rapidly growing IC industry in China will force design and EDA engineers, both inside and outside China, to explore, to innovate as well as to collaborate. With a large talent pool addressing unique challenges, who can say there will not be new technologies, methodologies and products emerging to change the rules of the global information technology landscape?

**Biography:** Prof. Shaojun Wei is the Dean of the Department of Microelectronics and Nanoelectronics, Tsinghua University, Member of National IC Industry Development Advisory Committee, Vice President of China Semiconductor Industry Association (CSIA), Fellow of Chinese Institute of Electronics (CIE).

Prof. Wei received Master degree in Engineering from Tsinghua University in 1984 and Doctor Degree in Applied Science in 1991 from the Faculté Polytechnique de Mons (FPMs), Belgium and then became the assistant professor in FPMs. He returned to China in 1995. His research interest includes high-level synthesis, embedded systems design and reconfigurable computing technology. He has published nearly 190 papers, one monograph and participated in the writing of three monographs.

Prof. Wei worked for Datang Telecom Technology Co., Ltd. successively as Vice-President, President & CEO from 1998 to 2005 and CTO of Datang Telecom Industry Group from 2005 to 2006.

Prof. Wei had won many awards including China National Technical Invention Second Prize, China National Science and Technology Progress Second Prize, China Patent Golden Award (SIPO and WIPO), Technical Invention First Prize (Ministry of Education, China), Electronic Information Science and Technology First Prize (CIE), Outstanding Youth Award (CAST), Science and Technology Progress First Prize (Beijing Municipal), etc

#### **SPEAKERS:**

Shaojun Wei - Tsinghua Univ., Beijing, China

4

#### **DESIGNER TRACK: EMBEDDED SYSTEMS AND SOFTWARE SOLUTIONS**

Time: 1:30 - 3:00pm | | Room: Ballroom E | | Event Type: Reviewed Presentations

Track: Embedded Systems, Design | | Topic Area: Embedded System Software, SoC &

Embedded System Architectures, Emerging Architectures & Technologies

#### **CHAIR:**

Andrew Putnam - Microsoft Corporation, Seattle, WA

#### **CO-CHAIR:**

Michael Brogioli - Network Native, Austin, TX

This ESS session explores topics in heterogeneous computing, virtualization, FPGA design and Neural Networks. These topics are presented as they pertain to the design and implementation of modern embedded computing systems and software solutions.

### 4.1 Behavior Sampling Based Fast Power Analysis for SSD Design (1:30)

Kwanghyo Ahn, Hyungwoo Lee, Dongeun Lee, Jongbae Lee - Samsung Electronics Co., Ltd., Hwaseong, Republic of Korea

#### 4.2 N2D2: A Deep Neural Networks Design, Optimization and Code Generation Framework for CoTS and Dedicated Hardware IPs (1:45)

**Olivier Bichler**, Alexandre Carbon, David Briand, Vincent Lorrain, Jean-Marc Philippe - CEA-LIST, Gif-Sur-Yvette, France

### 4.3 Using Virtual Platforms for Early Architectural Exploration: Experimentation on an Image Processing System (2:00)

Hubert Guérard - Space Codesign Systems, Montreal, QC, Canada Eric Jenn - IRT Saint-Exupery & Thales, Toulouse, France Guy Bois - Space Codesign Systems, Montreal, QC, Canada

### 4.4 The More the Merrier – Building Integrated Heterogeneous Virtual Platforms (2:15)

Jakob Engblom - Intel Corp., Stockholm, Sweden

### 4.5 Arch: A New Language for the Next Wave of Network-Connected Embedded Development (2:30)

Richard Moats, Bill Games - Network Native & Rice University, Austin, TX Michael Brogioli - Network Native, Austin, TX

### 4.6 Automating Communication of Complex Data in FPGA Accelerated Software Systems (2:45)

Adam Sapek - Microsoft Corporation, Redmond, WA

Andrew Putnam, Daniel Lo - Microsoft Research, Redmond, WA

Derek Chiou, Kalin Ovtcharov, Shlomi Alkalay - Microsoft Corporation,

Redmond, WA

Q & A Poster Session 2 Monday, June 19 5:00 - 6:00 - Exhibit Floor

Thank You to Our Sponsor

#### **WELCOME TO AUSTIN**

Austin is the capital of Texas, home of the University of Texas at Austin and gateway to the beautiful Hill Country. Shop in the one-of-a-kind boutiques that line South Congress and the 2nd Street district, or head out to hill country to relax in a world class destination spa.

More than 300 days of sunshine lend itself to a refreshing dip in Barton Springs or try stand-up paddle boarding on Lady Bird Lake. Find out more at austintexas.org.

5

#### **DESIGNER TRACK: EMPOWERING DESIGN**

Time: 1:30 - 3:00pm || Room: Ballroom F|| Event Type: Reviewed Presentations Track: Design, EDA || Topic Area: Low-Power & Reliability, Physical Design & DFM, Digital Design

#### CHAIR:

Badhri Uppiliappan - Analog Devices, Inc., Wilmington, MA

This session will focus on all considerations for power and reliability. Minimizing power at chip level will be a focus, as well as ensuring electromigration sign-off in large and complex designs.

#### 5.1 Resistance Driven Routing Methodology of Power Supply Network for Low Power and Multiple Voltage Design (1:30)

Makoto Minami, Mathieu S. Molongo, Kenji Aoyama, Chen Lingfeng, Zhu Xiaoke, Kouji Ishihara, **Nobuto Ono**, Shunichi Kuwata, Kazuhiro Miura - *Jedat, Inc., Tokyo, Japan*

Koutaro Hachiya - Jedat, Inc., Chuo-ku, Japan

#### 5.2 Cost Effective Super Cut-Off Power Gating Circuits (1:45)

**Insub Shin** - Samsung Electronics Co., Ltd., Gyeonggi-do, Republic of Korea

Jaehan Jeon - Cadence Design Systems, Inc., San Jose, CA Jun Seomun - Samsung Electronics Co., Ltd., Yongin, Republic of Korea Wook Kim, Kyungtae Do - Samsung Electronics Co., Ltd., Hwaseong-si, Republic of Korea

Jung Yun Choi - Samsung Electronics Co., Ltd., Yong-in, Republic of Korea

### 5.3 ESD 2kV HBM - Case Study on Connecting Signal IO Cells to Bumps on a Flip-Chip SoC (2:00)

Pritesh Pawaskar - Seagate Technology, LLC, Pune, India **Yehuda Smooha** - Seagate Technology, LLC, Allentown, PA Anant Narain - Apache Design, Inc., A Subsidiary of ANSYS, Inc., Noida, India

Shrikrishna N. Mehetre - Seagate Technology, LLC, Pune, India

### 5.4 Comprehensive Power Rail Constraint Verification for Large Analog Designs at Early Stage (2:15)

Shuichi Teramoto - Renesas System Design Co., Ltd., Kodaira-shi, Japan Hisato Inaba - Renesas System Design Co., Ltd., Takasaki-shi, Japan Kunihiro Yanaqida - Mentor, A Siemens Business, Shinaqawa-ku, Japan

### 5.5 Physics-Based Electromigration Assessment for Analysis of EM Degradation in 3D IC Test Structures (2:30)

**Jun-Ho Choy**, Valeriy Sukharev - *Mentor, A Siemens Business, Fremont, CA* Sandeep Chatterjee, Farid N. Najm - *Univ. of Toronto, Toronto, ON, Canada* Stéphane Moreau - *CEA-LETI Minatec, Grenoble, France*

#### 5.6 Machine Learning Based Electromigration Waiver System (2:45)

Ting Ku, Rex Lin - NVIDIA Corporation, Santa Clara, CA Ajay Baranwal, Norman Chang, Rahul Rajan, Kanishka De, Mallik Vusirikala - ASYS, Inc., San Jose, CA

Q &A Poster Session 2

Monday, June 19 5:00 - 6:00 - Exhibit Floor

Thank You to Our Sponsor

6

## IP TRACK: THE IP PARADOX: GROWING BUSINESS DESPITE CONSOLIDATIONS

Time: 1:30 - 3:00pm | | Room: Ballroom G | | Event Type: Panel | | Track: IP

Topic Area: General Interest

#### **MODERATOR**

Dan Nenni - SemiWiki.com, San Jose, CA

#### **ORGANIZER:**

Eric Esteve - IP-nest, Paris, France

The Design IP has become the largest category of EDA in 2016/17 (ESD Alliance, 2016 report), growing by 10% YoY in spite of the semiconductor industry affected by consolidation and exponential SoC development cost. What are the market forces that are fueling IP business growth? IP license price increases? Number of IP in an SoC? Make vs Buy trends? These forces can be linked with price, number of IP in a SoCs, technology node and/or make vs buy trends. Is injection of money from International funds creating short term growth?

#### **PANELISTS:**

Elias Lozano - Open-Silicon, Inc., San Jose, CA Sujoy Chakravarty - SilabTech, Bangalore, India Chengyu Zhu - Semconductor Manufacturing International Corp., San Jose, CA

Sanjive Agarwala - Texas Instruments, Inc., Dallas, TX

Thank You to Our Sponsor

#### DESIGNER TRACK: SAFE PLATFORMS AND SOLUTIONS APPLIED IN HIGHLY AUTOMATED DRIVING

Time: 3:30 - 5:00pm | | Room: Ballroom E | | Event Type: Invited Presentations Track: Automotive, Embedded Systems | | Topic Area: Emerging Architectures & Technologies, SoC & Embedded System Architectures, Codesign & System Design

#### **CHAIR:**

Selma Saidi - Univ. of Hamburg, Germany

#### **ORGANIZERS:**

Rolf Ernst - Technische Univ. Braunschweig, Germany Gerardo Daalderop - NXP Semiconductors, Eindhoven, The Netherlands

In many automotive applications, from Advanced Driver Assistance Systems (ADAS) to highly automatic and coordinated driving, high performance requirements have reached safety-critical, real-time architectures.

This entails a paradigm shift in programming and integration methods to meet tight timing and safety requirements demanded by safety standards, such as IEC 61508 or ISO 26262.

Consequently, to accommodate these partially contradictory requirements, new platforms and solutions from MPSoCs and software architectures to cyber-physical networking are necessary.

We begin with a short introduction to the field and continue with novel industrial solutions and research addressing the challenges.

In the first talk, NXP will present an architecture that applied in a next step-up in platooning including wireless communication and failoperational modes.

Next, Elektrobit will present a SW platform for automated driving capable of comfort and safety updates.

Finally, TUBS will show a HW architecture allowing smooth transition from Multi- to Manycore systems in automotive context.

#### 7.1 Architectures and Solutions Applied in Highly Automated Platooning (3:30)

Gerardo Daalderop - NXP Semiconductors, Eindhoven, The Netherlands Tjerk Bijlsma - TNO, Eindhoven, The Netherlands

Geoffrey Waters - NXP Semiconductors, Austin, TX Lars Reger - NXP Semiconductors, Hamburg, Germany

#### 7.2 The Multifaceted Platform: New HAD Software Functions From Development to Volume Production (4:00)

Sebastian Ohl - Elektrobit Automotive GmbH, Erlangen, Germany

#### 7.3 From Multi - to Manycore Systems in Safety-Critical **Automotive Applications (4:30)**

Adam Kostrzewa, Rolf Ernst - Technische Univ. Braunschweig, Germany

Thank You to Our Sponsor

8

#### **DESIGNER TRACK: GROWING IC DESIGN AND ECOSYSTEM IN CHINA: OPPORTUNITIES AND CHALLENGES**

Time: 3:30 - 5:00pm | | Room: Ballroom F | | Event Type: Panel | | Track: Design, EDA Topic Area: Digital Design, General Interest

#### **MODERATOR:**

Junko Yoshida - EE Times, Manhasset, NY

#### **ORGANIZER:**

Zhuo Li - Cadence Design Systems, Inc., Austin, TX Jason Xing - ICScape Inc., San Jose, CA

China has now become the largest semiconductor market in the world. About 1/3 of consumer electronic circuits are based on demand from China. While there is still high dependency for chip supplies from US and Europe, there is a growing trend that more chips are designed in China, from both design teams in big global companies, as well as fast growing domestic companies. The high growth rate now extends from traditional manufacturing and packaging sectors to the IC design area. According to some data sources, the CAGR of chip design sector from 2000 to 2015 is about 45%. China domestic chip industry is about 22% of global market share and contributes to the global semiconductor growth. At the same time, such growth is limited to certain types of chips, such as ASIC, communication chips, FPGA and some mixed-signal circuits, and there is clearly a shortage on high end IC designs. How does the growth in China change the chip design and manufacturing industry globally? Is that a threat or win-win for US and Europe IC design companies? Will consumer market in China boost global semiconductor industry? In this panel, the executives from design, manufacturing and EDA companies in China, as well as research directors from US and Europe will share their views on these questions and discuss opportunities and challenges for growing IC design and ecosystem in China.

#### **PANELISTS:**

Xiaoning Qi - Hangzhou C-Sky Microsystems Co. Ltd., Hangzhou, China Weiping Liu - Huada Empyrean Software Co., Ltd, Beijing, China Nanxiang Chen - China Resources Microelectronics Ltd., Wuxi, China Ahmed Jerraya - CEA Tech, Grenoble, France TianShen Tang - Semiconductor Manufacturing International Corp.,

Shanghai, China

Thank You to Our Sponsor

9

#### IP TRACK: MINIMIZING IC POWER CONSUMPTION: TOP DOWN OR BOT-TOM UP DESIGN METHODOLOGY. WHAT IS THE STARTING POINT?

Time: 3:30 - 5:00pm | | Room: Ballroom G | | Event Type: Panel | | Track: IP, Design Topic Area: Low-Power & Reliability

#### **MODERATOR:**

John Blyler - Electronic Design Magazine, Portland, OR

#### **ORGANIZER:**

Farzad Zarrinfar - Mentor, A Siemens Business, San Jose, CA

In this panel, implementation techniques and tradeoffs for designing ultra Low-power Semiconductor IP, SOCs, ASSPs, and ASICs will be discussed. These techniques are critical for devices requiring thermal management, are battery-powered and need package cost reduction. IP suppliers and EDA vendors now offer low-power IPs with optimization tools.

Topics such as FinFet and FDSOI devices will be compared with planar CMOS, power harvesting, and using UPF for low power implementation.

Designers apply reduced or Dynamic Voltage & Frequency Scaling, power shutdown, and retention logic. Typical low-power designs have over 30 different power modes and domains. Dual-rail memories operate in full power, partial power, or shutoff modes. Designs include isolation cells, level shifters, and retention cells with multiple modules in each power domain. Optimization of these techniques for various applications such as portable Gaming, IOT, Automotive, Wireless, Networking, wearable computing. low power techniques are paramount for differentiation and gaining market share.

Aditva Mukheriee - Microsoft Corporation, Mountain View, CA Tim Saxe - QuickLogic Corp., San Fransisco Bay Area, CA Abhishek Ranjan - Mentor, A Siemens Business, Noida, India Ronald Martino - NXP Semiconductors, Austin, TX Lluis Paris - Taiwan Semiconductor Manufacturing Co., Ltd., San Jose, CA Jon Adams - ON Semiconductor, San Jose, CA

Thank You to Our Sponsor

# DESIGNER/IP TRACK POSTER SESSION Time: 5:00 - 6:00pm | | Room: Exhibit Floor | | Event Type: Poster Session Track: Design, IP | | Topic Area: General Interest

During the poster presentation, you will interact directly with poster presenters in a small group setting.

As the limited time available in the Designer/IP Track session program was exceeded by the quantity of great submitted content, we present the following posters in the Designer/IP Track Poster Session held Monday, June 19 from 5:00 to 6:00pm on the Exhibit Floor.

#### 122.1 Converging Designs in Nanometer Era

Ambar Mukherji - Intel Corp., Bangalore, India Niraj A. Mehta - Intel Technology India Pvt. Ltd, Bangalore, India

#### 122.2 Novel Method for Test Time Reduction in Scan Optimization

George Antony - IBM Systems and Technology Group & Indian Institute of Technology Madras, Bangalore, India

Mary P. Kusko - IBM Corp., Poughkeepsie, NY Sridhar Rangarajan - IBM Corp., Bangalore, India Shrinivas Shenoy - IBM Corp., Bengaluru, India

#### 122.3 Programmable Repeater Station Approach for Hierarchical SoC Jasmeet Singh, Suresh Raman, Subbarao Govardhanagiri - Xilinx Inc.,

Hvderabad, India

#### 122.4 Flexible Hierarchy Management in the **IBM Microprocessor Flow**

Alex Suess - IBM Server and Technology Group, Poughkeepsie, NY Michael Kazda - IBM Systems and Technology Group, Poughkeepsie, NY Friedrich Schroeder, Peter Verwegen, Niels Fricke - IBM Deutschland Research & Development GmbH, Boeblingen, Germany

Thank You to Our Sponsors

#### 122.5 A Method for Efficient Design Closure Using **Incremental Synthesis**

Vinay K. Singh - IBM Corp., Bangalore, India George Antony - IBM Systems and Technology Group & Indian Institute of Technology Madras, Bangalore, India Sridhar Rangarajan - IBM Corp., Bangalore, India

#### 122.6 Reducing Noise Impact on Function by Isolation Routing

Michael Kazda - IBM Systems and Technology Group, Poughkeepsie, NY Dirk Müller - Univ. of Bonn, Germany Christian Schulte - IBM Systems and Technology Group,

Boeblingen, Germany

#### 122.7 SDC Exceptions Verification: Bridge Functionality and **Timing with Confidence**

Vlad Goldman - Marvell Semiconductor, Inc., Yokneam, Israel

#### 122.8 Next Generation Power Grid Prototyping and Package-**Aware Analysis of High-Current Transient Events**

Yiyong (Eason) Sun, Dawn M. Graves - Xilinx Inc., San Jose, CA Anusha Prakash - ANSYS, Inc., San Jose, CA

#### **DESIGNER/IP TRACK POSTER SESSION**

### 122.9 Effective CTS Strategy on Multi-Scenario Complex Clock Design

**Wei Wei** - Huawei Technologies Co., Ltd. & HiSilicon, Shenzhen, China Xiao Yong - Huada Empyrean Software Co., Ltd, Beijing, China

### 122.10 A Vectorless Methodology for Drop-Aware Early PDN Optimization of Scan Chains

**Arun James** - Broadcom Limited, Bengaluru, India Abhijith MV - ANSYS, Inc., Bangalore, India

#### 122.11 Prototyping of Power Grid in 7nm Designs

Yongchan Ban - GLOBALFOUNDRIES, Santa Clara, CA Jongwook Kye - GLOBALFOUNDRIES, Sunnyvale, CA

#### 122.12 Clock Trees with Low Process Variation - Part 2

Gary Ellis - Encore Semi Inc. & GLOBALFOUNDRIES, Norman, OK Mark Lasher - GLOBALFOUNDRIES, Williston, VT Bertram L. Bradley - GLOBALFOUNDRIES, Austin, TX Phillip Normand - GLOBALFOUNDRIES, Chippewa Falls, WI

#### 122.13 Timing Rule Verification Tool for Custom Circuit Macros

Ben Bowers, Josh Puckett - Qualcomm Technologies, Inc., Raleigh, NC

### 122.14 Timing Optimization by Utilizing Net-Based Target Congestion Ratios in Routing

Diwesh Pandey, - IBM Systems and Technology Group, Bangalore, India Sven Peyer - IBM Systems and Technology Group, Boeblingen, Germany Yaoguang Wei - IBM Corp., Austin, TX

### 122.15 Significantly Improving Place & Route Runtime by Minimizing Clocks/Register

Kalyan R. Hampapuram, **Venkatraman Ramakrishnan** - Texas Instruments India Pvt. Ltd., Bangalore, India

### 122.16 Securing an IP Product in the World of Automotive Validation

**Brian Eplett**, Randy Caplan - Silicon Creations, Suwanee, GA Emmanuel Peddi - Silicon Creations & IEEE, Suwanee, GA Greg Curtis - Mentor; A Siemens Business, Wilsonville, OR

### 122.17 Customising APIS IQ Software for ISO26262 Safety Analysis

**Krishnapriya C. Ramamoorthy**, David Addison - *Infineon Technologies UK Ltd.*, *Bristol*, *United Kingdom*

### 122.18 A Cost-Effective IP Integration & Design Restructuring Methodology for Large SoC Designs at RTL

Ishay Vaisid, Sara Hassar - Marvell Semiconductor, Inc., Yokneam, Israel **Sylvain Danjean** - DeFacTo Technologies, Grenoble, France Chouki Aktouf - DeFacTo Technologies, Moirans, France

#### 122.19 Augmentation of Static and Dynamic Checks for Electrical Verification of Mixed Signal Circuits

**Deepon Saha**, Krishnan T. Sukumar, Hariprasad TT - Advanced Micro Devices, Inc., Bangalore, India

#### 122.20 Custom Decap Analysis Flow for Accurate EM/IR Sign-Off

**Deepon Saha**, Hariprasad TT, Krishnan T. Sukumar - Advanced Micro Devices, Inc., Bagalore, India

### 122.21 Managing CSR Design Complexity Using a Single-Source, Unified-Flow Approach

**Dave Burgoon** - Microsoft Corporation, Fort Collins, CO Miguel Comparan - Microsoft Corporation, Redmond, WA

### 122.22 A High Level Synthesis (HLS) Design Flow for Scaling to Multiple IP, SoC, & Process Targets

**Hans L. Yeager** - Qualcomm Datacenter Technologies, Inc., Raleigh, NC Chris Platt - Qualcomm Technologies, Inc., Boulder, CO Anoop Lobo - Qualcomm Technologies, Inc., San Diego, CA

#### 122.23 Low Power IP Design Exploration Using RTL Power Flow

Ashish Mishra - Qualcomm India Pvt. Ltd., Bangalore, India Saurabh Shrimal - Mentor, A Siemens Business (India) Pvt. Ltd., Noida, India

Gopi Dabbadi - Qualcomm India Pvt. Ltd., Bangalore, India

#### 122.24 RTL Power Bug Review System

Sali Huang - MediaTek, Inc., Hsinchu, Taiwan

#### 122.25 Evolved Supply Set based UPF Methodology

Aman Jain - Seagate Technology, LLC, Pune, India

Thank You to Our Sponsors

#### **WELCOME TO AUSTIN**

Austin is the capital of Texas, home of the University of Texas at Austin and gateway to the beautiful Hill Country. As the Live Music Capital of the World, the city has a soundtrack all its own.

More than 250 live music venues flourish with rock, indie, pop and Tejano. Top notch restaurants with legendary barbeque and farm-to-table cuisine whet your appetite. Find out more at austintexas.org.

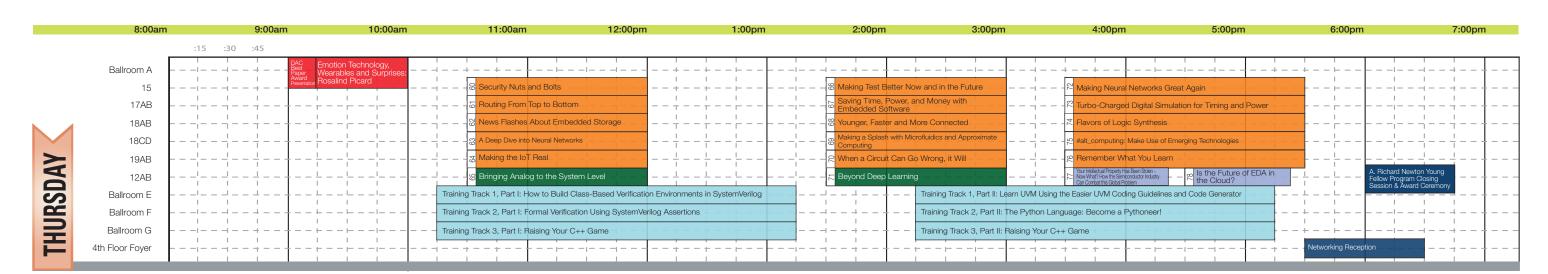

71

## TUTORIAL 1: LINUX BRING UP ON HETEROGENEOUS MULTIPROCESSOR SOCS

Time: 10:30am - 12:00pm | | Room: 17AB | | Event Type: Monday Tutorial

Track: Embedded Systems, IP | | Topic Area: Embedded System Software, SoC &

Embedded System Architectures, Emerging Architectures & Technologies

#### **ORGANIZER:**

Larry Lapides - Imperas Software Ltd., Thame, United Kingdom

Heterogeneous multiprocessor SoCs are becoming more common for use in application areas such as advanced driver assistance systems (ADAS) and autonomous vehicles, networking, industrial automation, security, video analytics and machine learning. These SoCs often have GPUs and/or hardware accelerator units that work together on a common set of data, however, the simplest coherent processing systems use multiple clusters of CPUs. These CPU clusters can be homogeneous, or heterogeneous, such as with ARM's big.LITTLE configuration or Imagination's MIPS I6500 architecture.

Linux has become the general purpose operating system of choice for embedded systems, and now for these heterogeneous multi-cluster architectures Linux needs to be modified to support the coherence between the clusters, as well as whatever differences exist between the clusters in terms of number of processors, processor type, and other features and capabilities. Most vendors use an open source Linux distribution from their processor IP vendor, then build a custom distribution representing the cluster/processor configuration and device tree supported for the specific SoC. This custom Linux distribution needs to include the necessary drivers for the peripherals on the SoC, as well as supporting other customizations and unique features. Obviously, this gets quite complex, and the complexity keeps increasing with increasing device complexity, including coherence.

This need to port, customize and bring up Linux on these heterogeneous SoCs requires significant engineering effort by the SoC developer. Also, their customers do not always reward this effort by paying more for the

SoCs. So how can the semiconductor vendors make this Linux task more efficient? What are the best practices for Linux porting and bring up on heterogeneous multi-cluster/multiprocessor SoCs?

This tutorial is presented in two sections. In the first section (Imagination Technologies), the various components of the Linux distribution are covered, including the basic Linux kernel, device trees and other customizations, SMP variations and drivers, both static and dynamic. Coherency for multi-cluster architectures is also discussed. The methodology used for bring up of the Linux kernel, starting with boot loaders including U-boot, on hardware is presented.

The second section (Imperas) discusses the development of a robust test environment using virtual platform technology. The virtual platform provides a complementary approach to porting and bring-up on hardware. The benefits of controllability, observability and repeatability for virtual platform use are covered. Automated testing, such as needed for an Agile Continuous Integration (CI) development and test methodology is discussed. Specific OS-aware tools are also highlighted, plus other tools such as non-intrusive memory monitors, the use of software assertions, and code and functional coverage techniques for the operating system and drivers.

#### **SPEAKERS:**

John Min - Imagination Technologies Ltd., Santa Clara, CA Simon Davidmann - Imperas Software Ltd., Thame, United Kingdom

**T2**

#### **TUTORIAL 2: SECURITY VALIDATION IN MODERN SYSTEMS-ON-CHIP**

Time: 10:30am - 12:00pm || Room: 18AB|| Event Type: Monday Tutorial Track: Security || Topic Area: Test & Verification, SoC & Embedded System Architectures

Modern systems-on-chip (SoCs) implement many security features to protect various assets like end user data, keys, fuses and OEM assets. As hardware security features and related attacks are increasing, functional validation of these security features is proving inadequate to address these challenges. While functional validation ensures proper functionality of the product, security validation allows for a more secure and robust product by evaluating features with security implications, analyzing the security impact and business risk of bugs/vulnerabilities that are discovered, and verifying bug fixes.

In this tutorial, using a generic System on Chip (SoC) as an example, we describe a security assurance methodology, some recent research results and discuss some open problems for the hardware security community. The focus areas of the tutorial are based in part on the learnings from security evaluations performed on commercial (Intel) products as well as our own expertise. This tutorial will be organized as follows:

Part I (Security Architecture): To lay foundation for the security assurance process, we describe the general security architecture features such as access control, isolation and cryptographic primitives using a simple and generic SoC architecture. We will describe the security objectives, security requirements of this SoC, the adversary model and the threat model under consideration.

Part II (Common HW Security Vulnerabilities): We will describe the concepts of vulnerability analysis and determine the severity of some

example hardware and firmware vulnerabilities. We will suggest a generic classification of hardware security vulnerabilities and common mitigation techniques.

Part III (Methodology for SoC Validation): We describe our methodology and best known methods for SoC security validation. We first show how SoC security requirements are translated into specific validation objectives. We will then discuss tools and techniques -- such as randomized testing and formal/semi-formal methods for information-flow verification -- that can be used to ensure these objectives are met by the SoC. We will conclude with a discussion of open research challenges in SoC security validation.